# Physical Design Challenges in Modern Heterogeneous Integration

張耀文 Yao-Wen Chang

ywchang@ntu.edu.tw http://cc.ee.ntu.edu.tw/~ywchang National Taiwan University March 14, 2024

### **Acknowledgements**

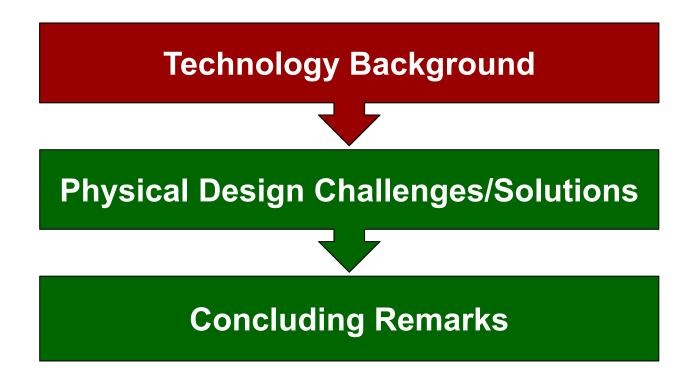

### Outline

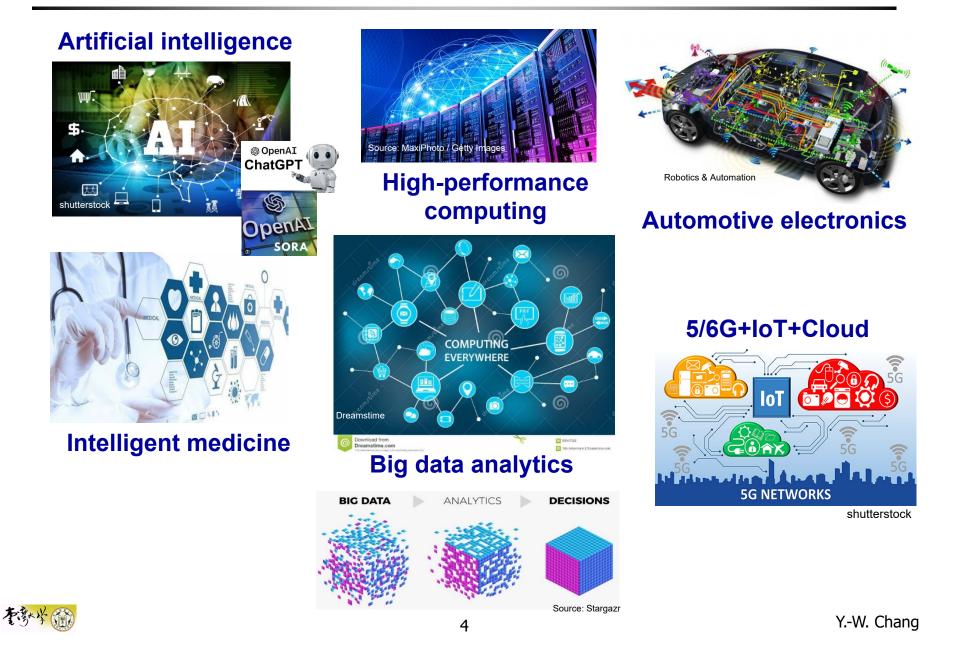

# **Technology Drivers**

#### **Technology Options for Achieving PPA Target**

Higher <u>Performance</u> Lower <u>Power</u> Smaller Area

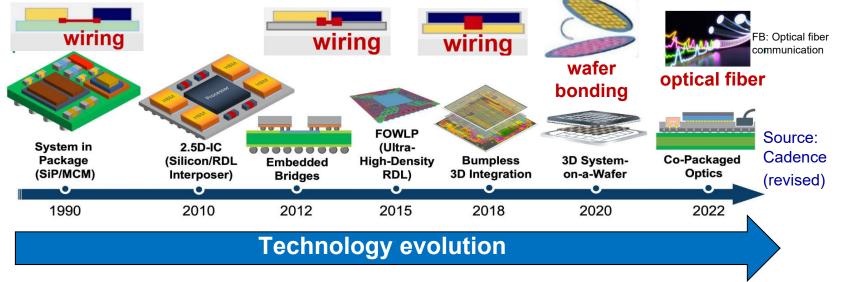

MtM More-than-Moore (MtM) Heterogeneous Integration 2.5D/3D Packaging RF/MEMS/sensor/analog Optical component

#### More Moore (MM)

**Beyond CMOS**

Pixtastock.com

Continued ScalingNew DevicesFinFET/Nanosheet/CFETGaAs/SiC/GaNMultiple patterning/EUV/DSAFerroelectric (FeFET)Backside power deliveryGraphene (GFET)

ΜN

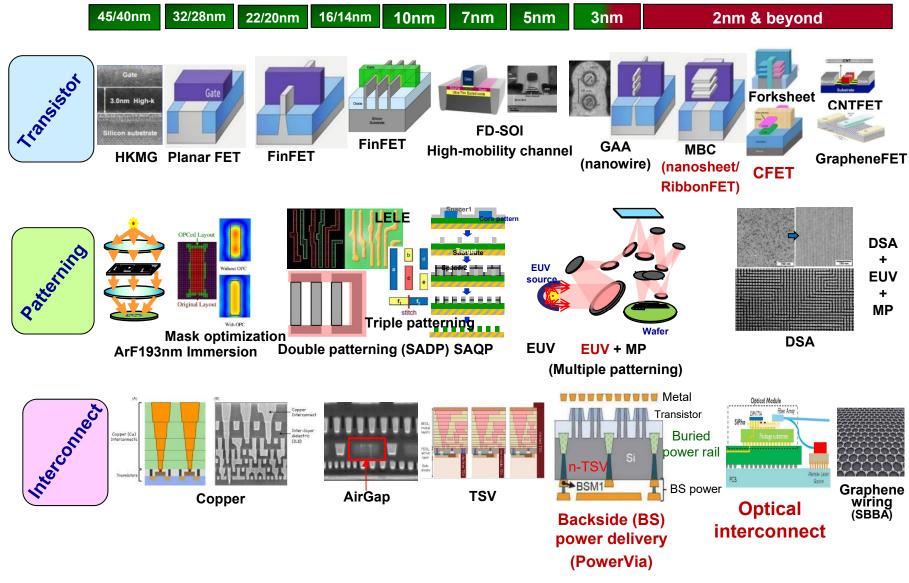

### **More Moore Technology Landscape**

#### **More-than-Moore Heterogeneous Integration**

- Economic advantages of More-Moore scaling are getting smaller (high manufacturing costs with advanced transistors, EUV, etc.), making the More-than-Moore trends more obvious.

- Heterogeneous integration with 3D stacking is promising with better system PPA, form factor, functionality, etc.

- Issues: complexity, yield, heat, interconnect cost, mechanical stress, testing, standardization, etc.

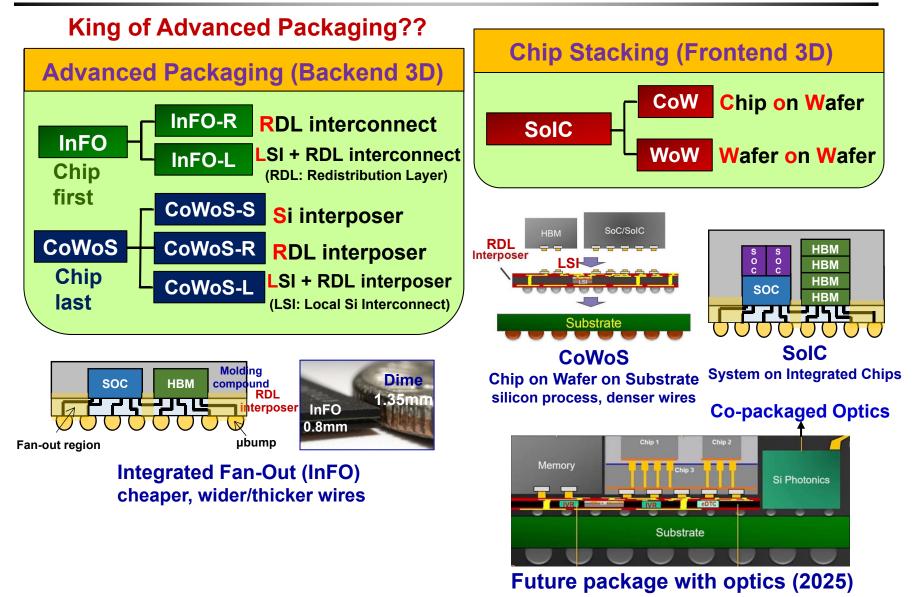

## **Advanced Packaging for TSMC's Success**

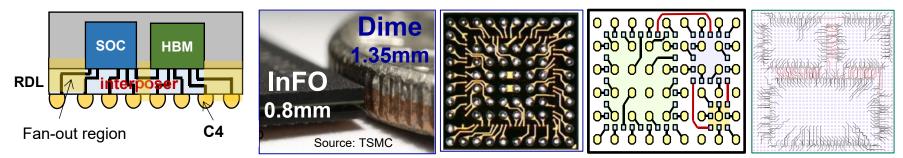

• Dr. Morris Chang (2016): InFO is key for TSMC to beat Samsung for Apple's A10 chip orders

BARRON'S TSMC Will Regain Apple In A10, InFO

First published InFO package router [Lin et al., ICCAD'16], US Patent 9,928,334, 2018 (with AnaGlobe)

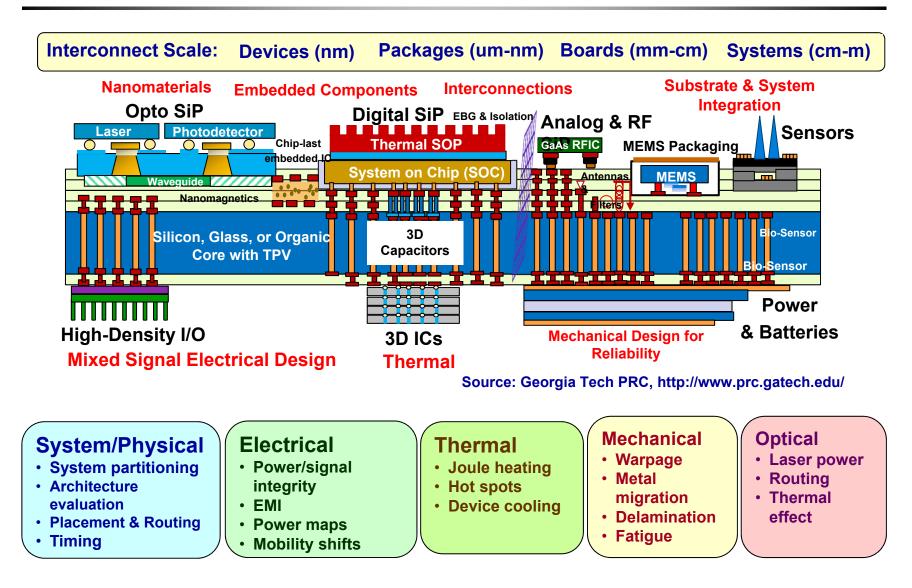

#### **Heterogeneous Integration & Multi-Physics Domains**

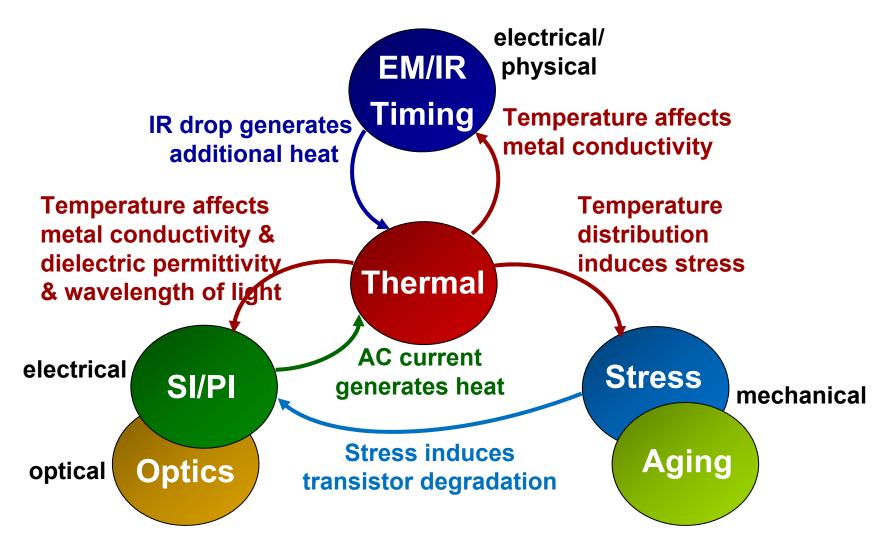

### **Multi-Physics Interactions**

Source: TSMC/Ansys (w. revision)

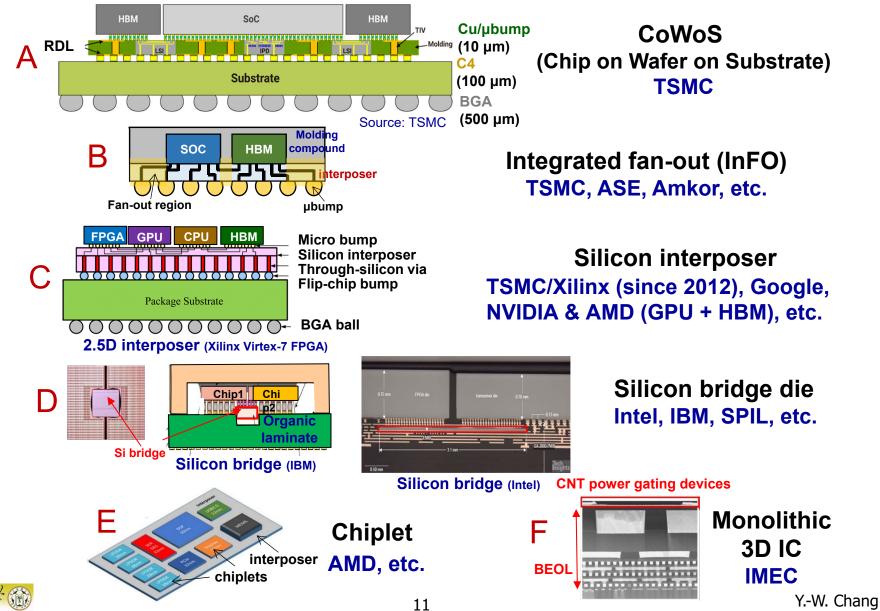

#### **Multiple Options for Heterogeneous Integration (HI)**

### **TSMC 3D Fabric**<sup>TM</sup> (since August 2020)

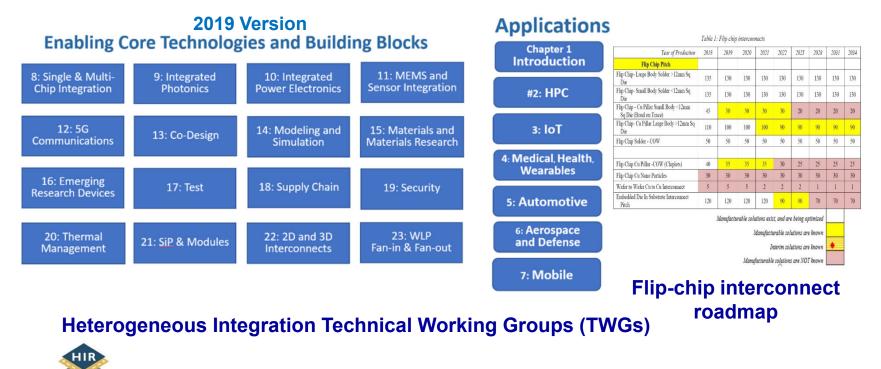

# **Heterogeneous Integration (HI) Roadmap**

• HI Roadmap since 2015 vs. ITRS & IRDS Roadmaps

HETEROGENEOUS Source: HIR Roadmap, 2019 (latest: 2023)

ITRS: International Technology Roadmap for Semiconductors (1998-2015) IRDS: IEEE International Roadmap for Devices and Systems (2016-)

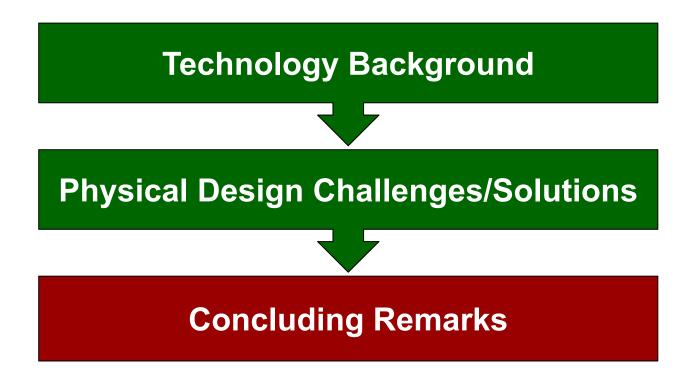

### Outline

# **Multi-Domain Challenges & Opportunities**

| System     | <ul> <li>System-level HI modeling &amp; simulation, heterogeneous device applications &amp; computing</li> <li>Power/performance/thermal/cost analysis for heterogeneous platforms</li> <li>Architecture with HI components, cost evaluation &amp; decision, hardware security &amp; reliability</li> </ul>     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Physical   | <ul> <li>3D partitioning, floorplanning, placement, routing, post-layout optimization (RDL routing)</li> <li>Package-/board-level routing, chip-package-board co-design (bump-aware design)</li> <li>Cross-domain timing analysis/optimization, chip/board/system &amp; 3D IC test, DFT connectivity</li> </ul> |

| Electrical | <ul> <li>3D power/signal integrity &amp; EMI prevention (PTH), buried power rail, stacking P/G network</li> <li>Stacking STA (cross dies) &amp; electrostatic discharge (ESD), inter-die coupling, substrate RLC</li> </ul>                                                                                     |

| Thermal    | <ul> <li>Stacking interconnect/full-system thermal analysis &amp; electromigration reliability</li> <li>Joule heating, hotspot detection &amp; handling, device cooling</li> </ul>                                                                                                                              |

| Mechanical | <ul> <li>Warpage/delamination/stress-aware optimization</li> <li>Metal migration simulation and optimization, fatigue reliability</li> </ul>                                                                                                                                                                    |

| Optical    | <ul> <li>Optical routing, thermal-aware power device placement, electrical &amp; optical co-design</li> <li>System-based optical device analysis &amp; optimization, laser power network, reliability</li> </ul>                                                                                                |

# **3D System-level Partitioning**

- Partition mixed-logic and -memory into multiple dies with different technologies for PPA optimization

- Device sizes & design rules change with different die assignment, NOT just min-cut partitioning!

- Must consider process technologies for multiple dies and corresponding interconnect/via/bump parameters for the overall cost optimization

System-level partitioning, planning, aggregation, and optimization

Source: Cadence

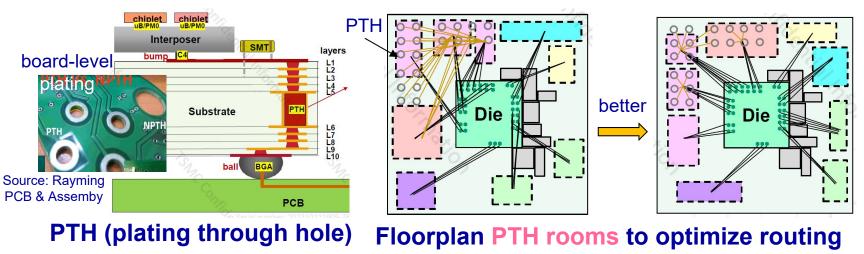

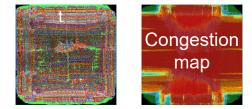

# **Cross-physics-domain Floorplanning**

- Integrating dies into an advanced package may suffer from severe electrical, thermal, and mechanical effects, e.g., stress, warpage, substrate noise, Joule heating, and delamination.

- A PTH (plating through hole) connecting a bump to a ball may induce severe EMI (electromagnetic interference) problems

- Must meet constraints: larger pitch for EMI, constrained regions, etc.

- Floorplan PTH rooms (locations, aspect ratios, etc.) of holes for better bump-PTH-ball routing

Source: TSMC

Source: TSMC

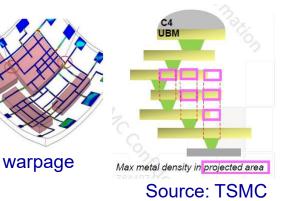

#### **Mechanical Issue: Warpage-aware Floorplanning**

- Hsu, Chung, and Chang, "Transitive closure graph-based warpage-aware floorplanning for package designs," ICCAD'22

- Mismatch in coefficients of thermal expansion between Si (die) & laminate substrate (interposer) causes thermo-mechanical stress and warpage

- Warpage modeling: Suhir's theory; floorplanning: TCG; simulation: ANSYS & Moldex3D

w(x)die interposer  $w(x) = \frac{t\Delta\alpha\Delta T}{2\lambda D} \left(\frac{1}{2}x^2 - \right)$  $\frac{\cosh kx - 1}{k^2 \cosh kl}$ **Traditional TCG-based** floorplanning  $\cosh kx - 1 > 0$  m<sub>7</sub> t: thickness  $k, D, \lambda$ : material related coefficients  $\Delta T$ : the temperature difference between initial temperature and final temperature  $\Delta \alpha$ : difference of coefficient of thermal TCG perturbation: Peripheralize  $m_6$ expansion

Warpage-aware TCGbased floorplanning

Suhir, "Interfacial stresses in bimetal thermostats," J. Appl. Mech., 1989.

(mm)

0.073

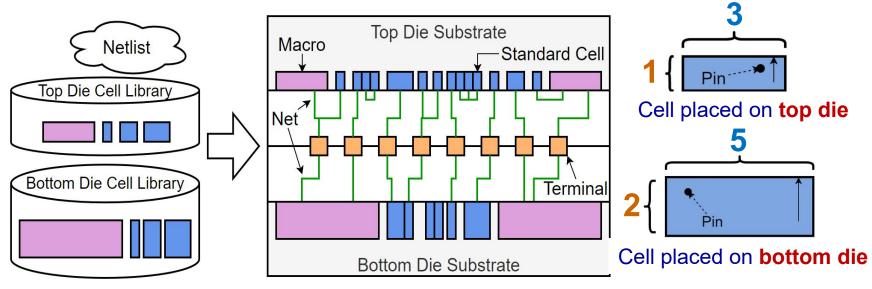

# Multi-die, Multi-technology Placement

- Dies integrated into a package could be fabricated with different technology nodes, so block (standard cell or macro) sizes are changed "dynamically" with die assignments.

- Signals are connected by hybrid bonding terminals.

- Chicken-and-egg challenge: Block dimensions change with die assignments.

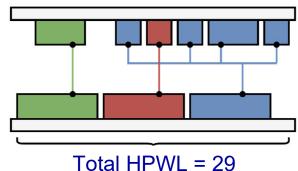

# 2023 ICCAD 3D F2F Placement Contest

- Input

- Netlist (including macros and standard cells)

- Cell libraries

- Terminal cost

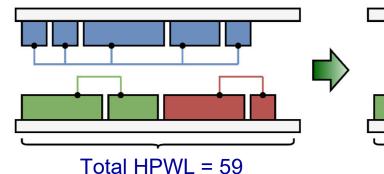

#### Objective: minimize the scoring function

$HPWL_{top} + HPWL_{bottom} + N_{term}C_{term}$ Total Wirelength Terminal Cost

- Constraints

- Non-overlapping blocks

- Spacing between terminals

- Maximum utilization rates on each die

2023 CAD Contest @ ICCAD NTU: 1<sup>st</sup> Place

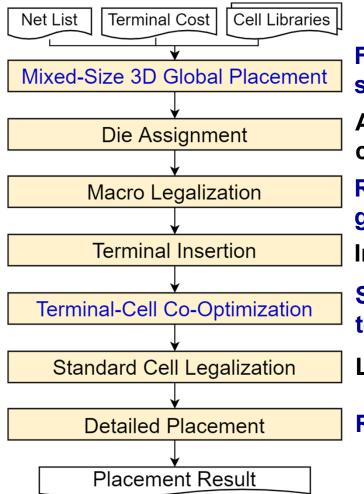

### **Our Placement Framework**

• Chen, et al., "Mixed-size 3D analytical placement with heterogeneous technology nodes," DAC'24 (1<sup>st</sup> Place at the 2023 ICCAD CAD Contest).

Find the desired positions for each macro & standard cell using 3D analytical placement.

Assign each component to its closest die, considering die utilization constraints.

Remove macro overlaps using constraint graphs and integer linear programming.

Insert terminals to current optimal positions.

Simultaneously optimize the standard-cell & terminal positions using analytical placement.

Legalize standard cells using Abacus & Tetris.

**Refine cell and terminal position further.**

# **3D Analytical Placement**

• Formulate an unconstrained optimization problem

min  $W(x,y) + \alpha Z(z) + \lambda N(x,y,z)$ Wirelength Terminal Cost Density

Use our Weighted-Average model [Hsu, Chang, Balabanov, DAC-11, TCAD-13; US Patent, 2014] for wirelength optimization

$$W(\mathbf{x}, \mathbf{y}) = \sum_{e \in E} \left( \frac{\sum_{v_{i \in e}} x_i \exp(x_i/\gamma)}{\sum_{v_{i \in e}} \exp(x_i/\gamma)} + \frac{\sum_{v_{i \in e}} x_i \exp(-x_i/\gamma)}{\sum_{v_{i \in e}} \exp(-x_i/\gamma)} + \frac{\sum_{v_{i \in e}} y_i \exp(y_i/\gamma)}{\sum_{v_{i \in e}} \exp(y_i/\gamma)} + \frac{\sum_{v_{i \in e}} y_i \exp(-y_i/\gamma)}{\sum_{v_{i \in e}} \exp(-y_i/\gamma)} \right) \\ \alpha Z(\mathbf{z}) = \sum_{e \in E} (\alpha + w_e) \left( \frac{\sum_{v_{i \in e}} z_i \exp(z_i/\gamma)}{\sum_{v_{i \in e}} \exp(z_i/\gamma)} + \frac{\sum_{v_{i \in e}} z_i \exp(-z_i/\gamma)}{\sum_{v_{i \in e}} \exp(-z_i/\gamma)} \right) \quad \begin{array}{l} \alpha: \text{ Via cost} \\ w_e: \text{ Net weight} \end{array}$$

- Apply ePlace-3D for density control [Lu et al., ISPD-16]

$$\begin{split} N(\mathbf{x}, \mathbf{y}, \mathbf{z}) &= \frac{1}{2} \sum_{v_i \in V} q_i \psi_i(\mathbf{x}, \mathbf{y}, \mathbf{z}) & q_i : \forall \mathbf{c} \\ \xi(\mathbf{x}, \mathbf{y}, \mathbf{z}) &= \left( -\frac{\partial \psi}{\partial x}, -\frac{\partial \psi}{\partial y}, -\frac{\partial \psi}{\partial z} \right) & \xi : \mathsf{E} \end{split}$$

$q_i$ : Volume of cell *i*  $\psi$ : Potential function  $\xi$ : Electric field

- Optimize the objective function using gradient descent

- Increase  $\lambda$  gradually to reduce the density to find the desired macros & standard cell positions (*x*,*y*,*z*)

22

# **Die Assignment**

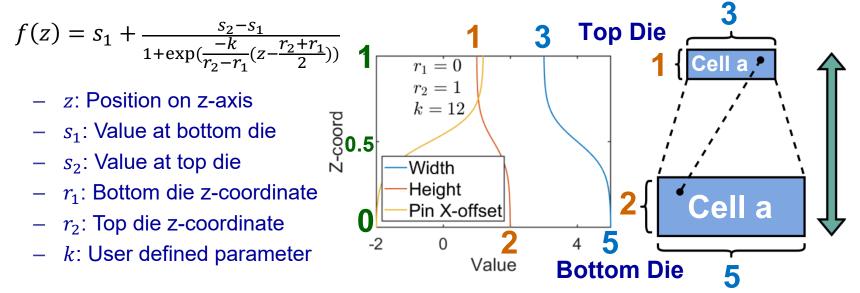

Relax the discrete assignment variable & use a sigmoid function to achieve smooth shape transition

#### • Partition the network using low-pin nets

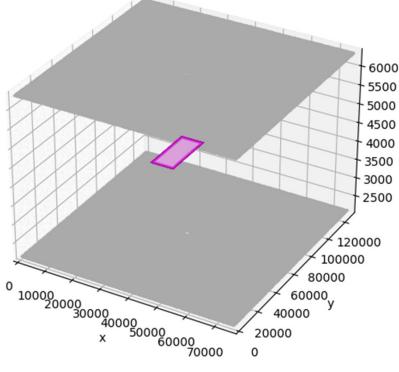

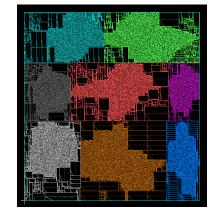

### **Demo: 3D Mixed-Size Global Placement**

- Benchmark: Case4

- \_ #macros: 32

- \_ #standard cells: 740,211

- \_ #nets: 758,860

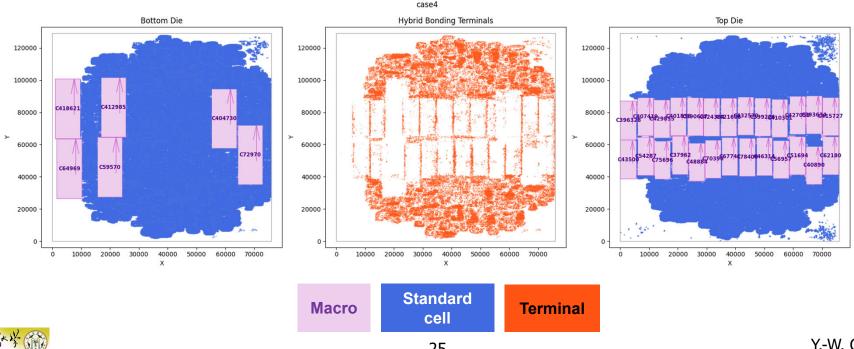

#### **Final Placement Result**

- Benchmark: Case4

- \_ #macros: 32; #standard cells: 740,211; #nets: 758,860

- Results

- Top-die wirelength: 864,717,801

- Bottom-die wirelength: 181,388,384

- Terminal cost:  $160,993 \times 10 = 1,609,930$

25

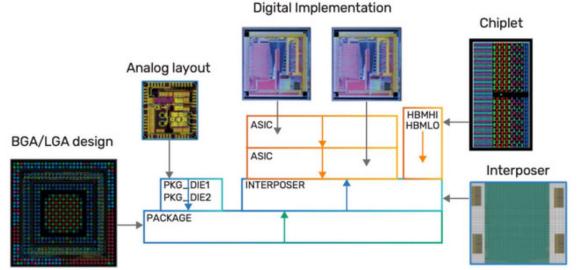

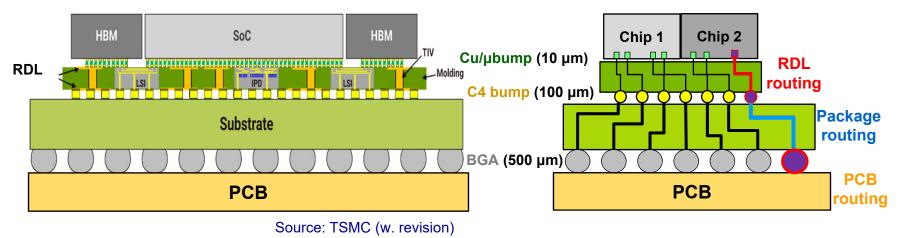

# **Package/PCB Routing**

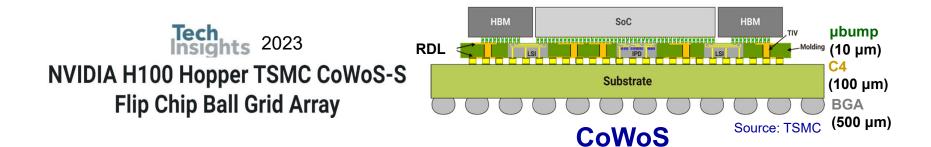

- Modern packages require high-performance connections among chiplets through multi-layer redistribution layer (RDL) interposers or substrate (e.g., CoWoS, InFO).

- Use RDLs to connect I/O pads (chip) to bump pads (package) to achieve better quality (e.g., more areas for I/Os, higher performance interconnections, better signal integrity and robustness)

- The rising complexity requires any-obtuse-angle routing to consider complex design rules

- Consider complex via stacking rules, irregular vias, inline/staggered bumps, max. metal density for reliability, differential pairs, shielding, etc.

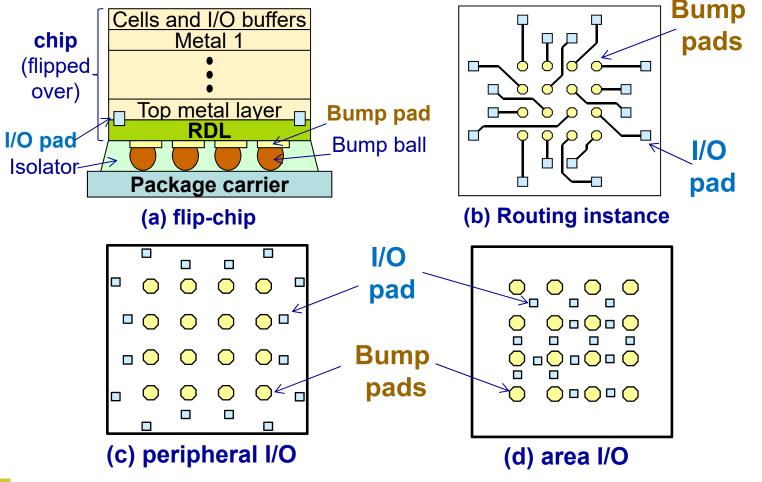

# **Flip-Chip RDL Routing**

- Flip-chip routing routes I/O pads to bump pads on RDL

- Two types of packages: (a) peripheral-I/O; (b) area-I/O

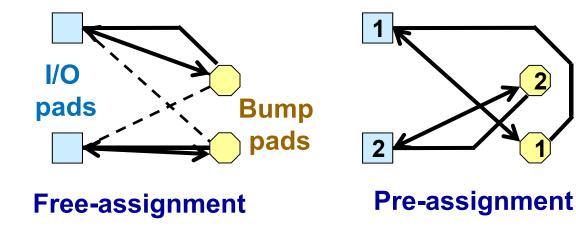

### **Free- vs. Pre-assignment Routing**

- Free-assignment routing

- Each bump pad can be connected to any I/O pad

- Router can assign each I/O pad to a bump pad

- Pre-assignment routing

- Connections between I/O and bump pads are predefined

- Router must connect a bump pad to its pre-assigned I/O pad

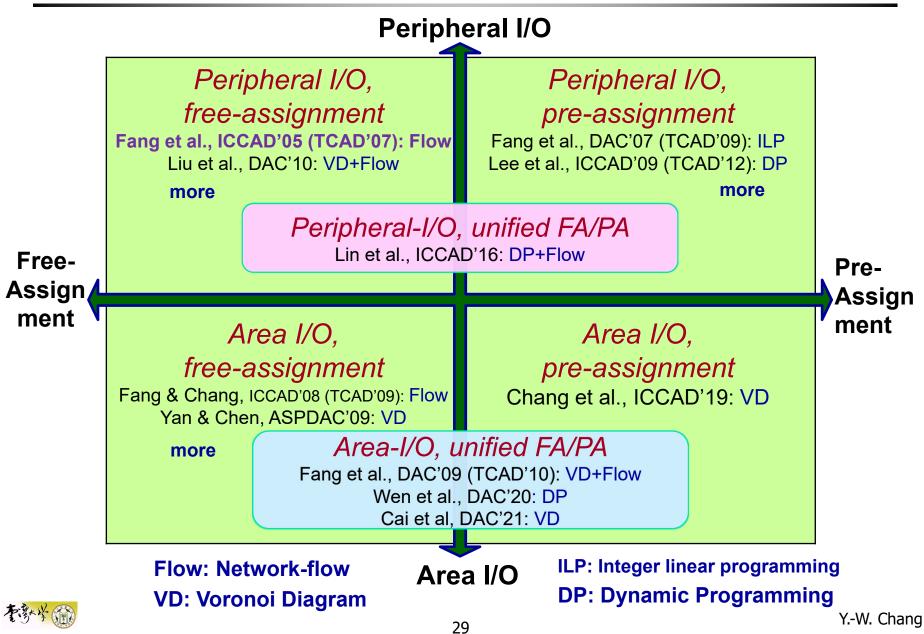

### **RDL Routing Classification & Techniques**

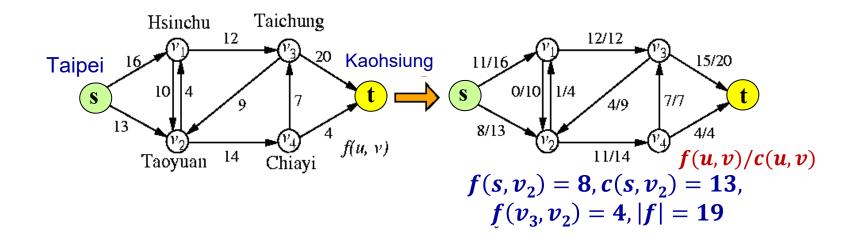

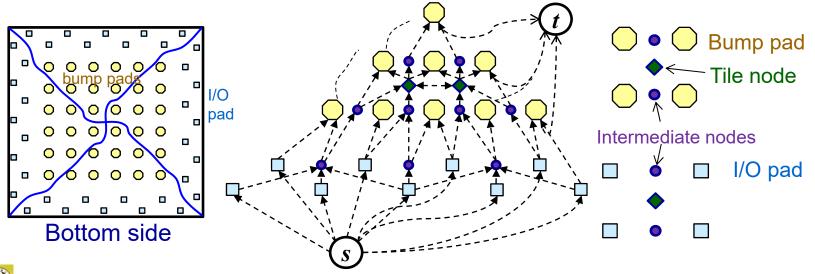

#### **Network Flow Formulation**

- Network flow problem: Given a flow network *G* with source *s* & sink *t*, find a maximum flow from *s* to *t*.

- Network flow formulation is useful for modeling resource assignment (supply-demand) problems.

- Key limitation: Control only the total flow, but not the individual flow at a specific node/edge (NP-complete multi-commodity flow problem)

#### **Network Flow for Free-assignment Routing**

- Most existing works are based on Minimum-Cost Maximum-Flow (MCMF) [Fang et al., ICCAD'05 & more]

- Divide a chip into four regions & route region by region

- I/O pad  $\rightarrow$  source node

- Bump pad → sink node

- Wire  $\rightarrow$  unit flow

- ─ Max-flow → highest routability

- ─ Min-cost → shortest wirelength

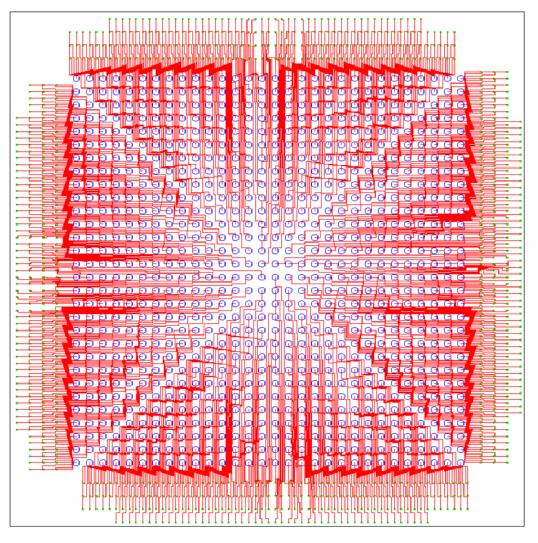

#### **Peripheral I/O, Free-assignment Routing Result**

Circuit: fs900

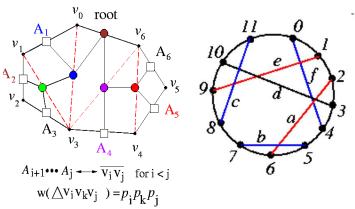

#### **Dynamic Programming (DP) for Pre-assignment Routing**

- Utilize the regularity of the flip-chip structure to achieve better solutions [Lee et al., ICCAD'09, TCAD'12]

- DP works best on linearly ordered objects that cannot be rearranged!!

- Examples: Characters in a string, matrices in a chain, left-to-right order of leaves in a search tree, points on a line/polygon/circle boundary

- Apply DP for pre-assignment routing

#### String: NTUEE

**Matrix chain**  $((A_1 (A_2 A_3))((A_4 A_5) A_6))$

Points on a line/polygon/circle boundary

# "Da Vinci Code" between Japan and Taiwan

#### 2010 Design Automation Conf. (DAC'10)

Dr. Kazutoshi Wakabayashi Yao-V <sup>(NEC)</sup> Longest Common Subsequence Similarity: 50%+!!

#### Yao-Wen Chang (NTU)

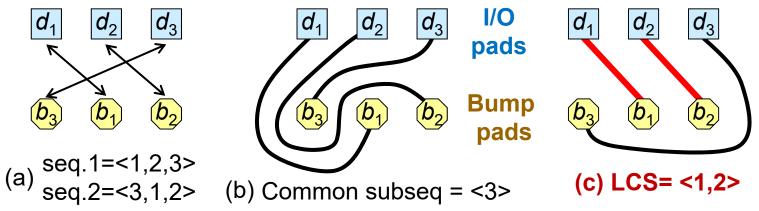

# **Detours Minimization by DP**

- DP to minimize detours for pre-assignment routing

- Longest common subsequence (LCS) computation

• Maximum planar subset of chords (MPSC) computation

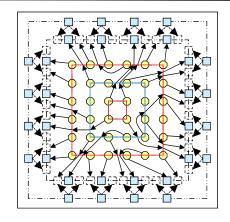

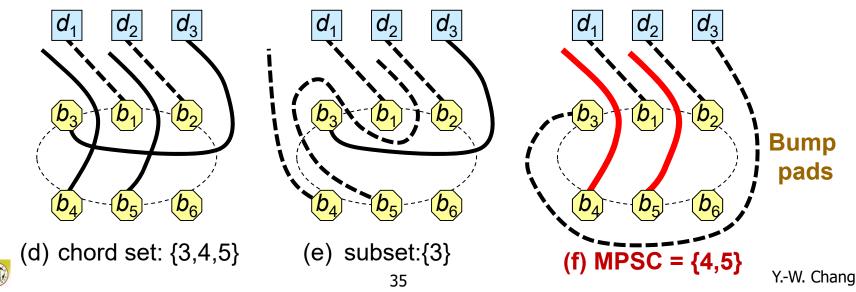

# **Pre-assignment Ring-by-Ring Routing**

- Identify feasible sequences for I/O pads and apply LCS

- Decompose chip into rings of bump pads and route from inner rings to outer rings

- Keep applying MPSC between two adjacent rings (red ring & blue ring)

—— current ring —— preceding ring

Achieve over 100X speedups than ILP with better quality!!

### **Demo: Circuit fc2624**

📼 Corner Stitching GUI System

- - X

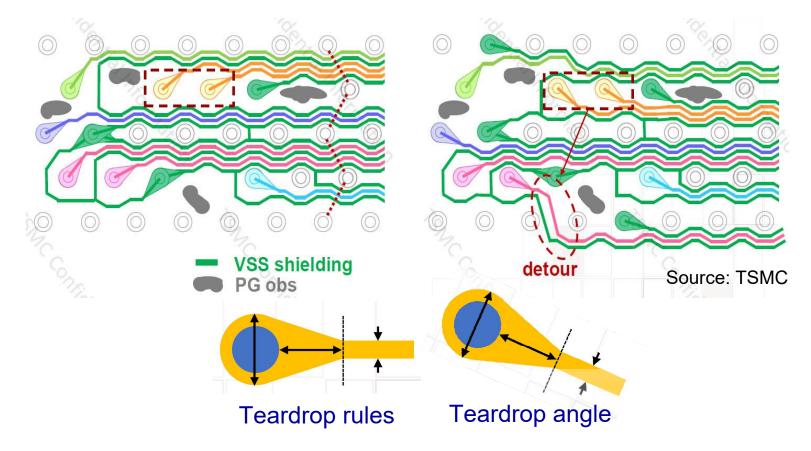

### **Any-obtuse-angle Routing**

- Need any-obtuse-angle routing to maximize flexibility

- Plan teardrop angles to maximize the routability

- Local teardrop angles could affect far-away connections

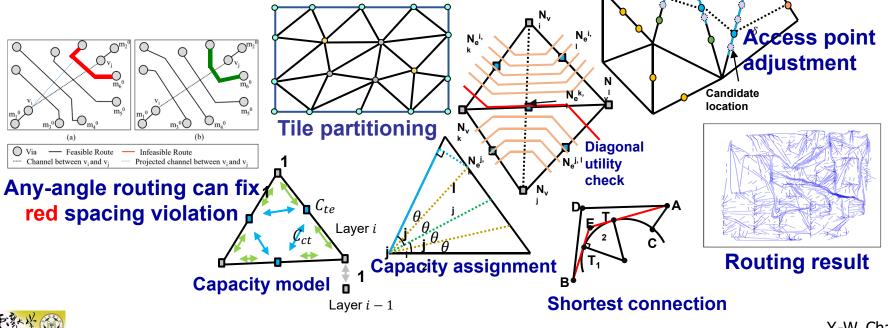

# **Any-obtuse-angle Package Routing**

- Chung et al., "Any-Angle Routing for Redistribution Layers in 2.5D IC Packages," DAC'23

- 1st any-angle router with multiple RDLs

- Apply Delaunay triangulation for tile partitioning

- Model intra- and inter-tile capacity to generate routing guides

- Apply dynamic programming-based access point adjustment to route multiple nets simultaneously

- Achieve the best published routability

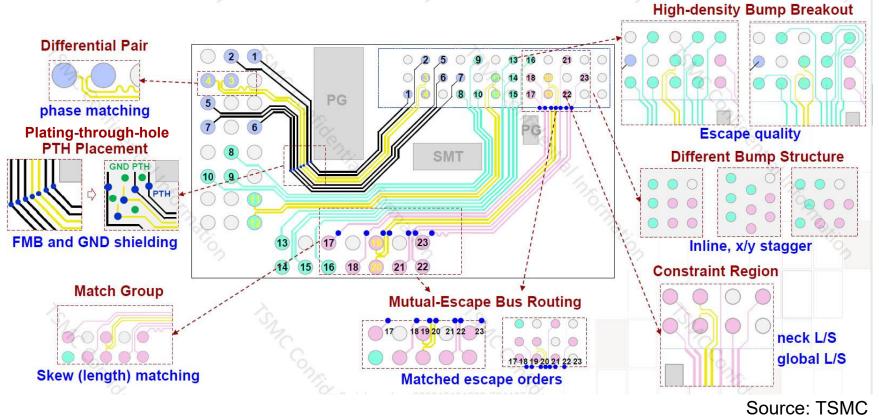

### **General Package Routing Considerations**

- Differential pairs (for phase matching), plating-through-hole (PTH) placement with shielding, length matching for skew, matched escape orders for bus routing, constrained regions, inline/staggered bump structures, bump breakout, etc.

- More: irregular vias, max. metal density for reliability, etc.

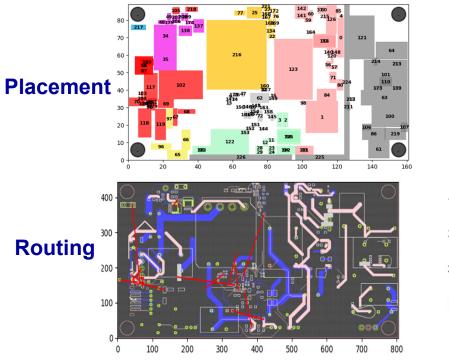

### **PCB Placement and Routing**

- Place irregular-shaped 3D components

- Route signal/PG wires of different widths

- Considerations: component orientations, diverse wire widths, dynamic spacing rules, power loop topologies, heat sink insertion, restricted areas, etc.

**Irregular 3D components**

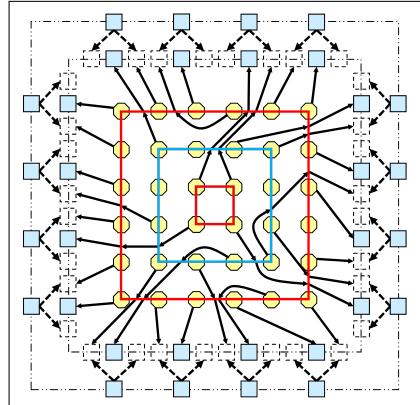

### **Chip-Package-Board Co-Design**

## **Chip-Package-Board Co-Design**

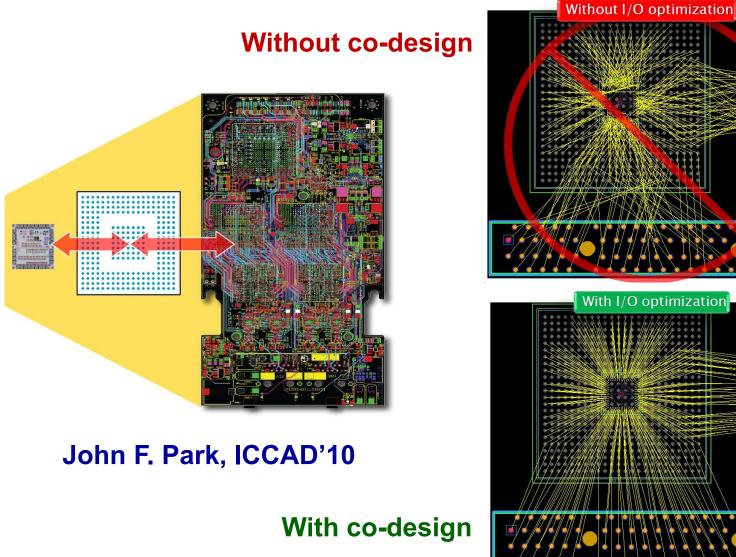

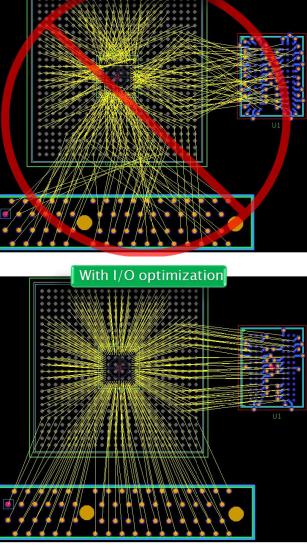

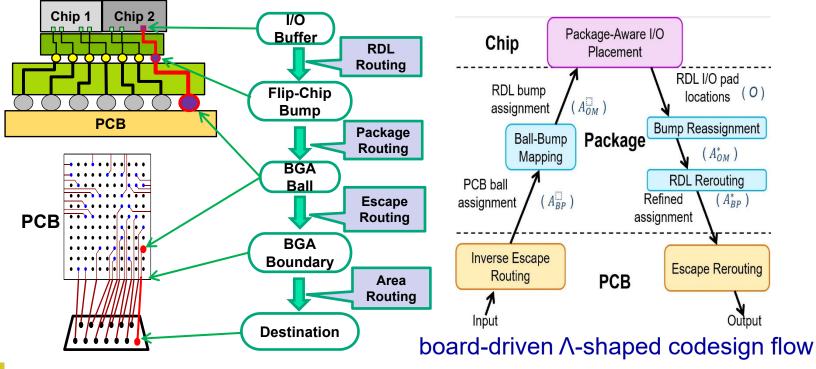

- Lee and Chang, "A chip-package-board co-design methodology," DAC'12 (Fang, Ho, and Chang, ICCAD'08)

- Route a signal from an I/O buffer, to a flip-chip bump (RDL routing), and finally at a BGA ball (package routing), ready for PCB connection

- Board-driven Λ-shaped codesign flow: Inverse escape routing (PCB), ball-bump mapping (package), package-aware I/O placement (chip), bump reassignment & RDL rerouting (package), escape rerouting (PCB)

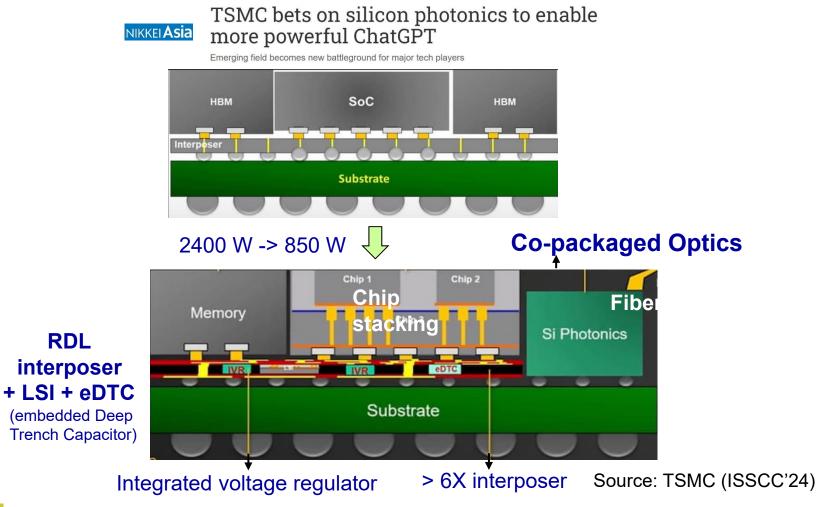

# **Co-packaged Optics (CPO)**

• TSMC has announced to integrate silicon photonics components into its advanced package by 2025

# **Optical Routing**

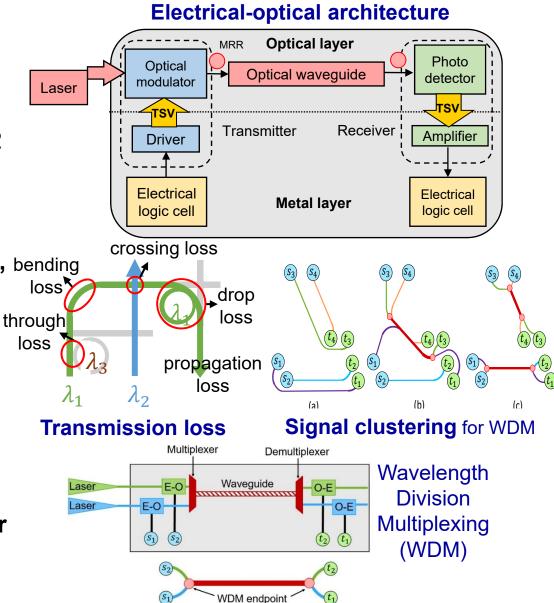

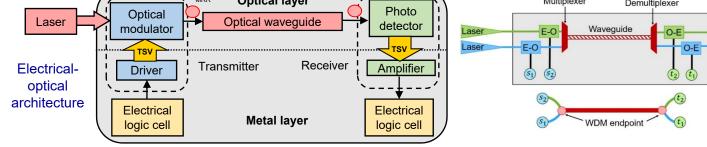

- Lu, Yu, Chang, "On-chip optical routing with provably good algorithms for path clustering and assignment," *TCAD*, 2022

- Allows a connection in any direction & signal crossings w. higher bandwidth, lower power, bending and faster speed

- Transmit signals on shared waveguides

- Need signal clustering to better use WDM (Wavelength Division Multiplexing)

- Minimize transmission loss & wavelength power

45

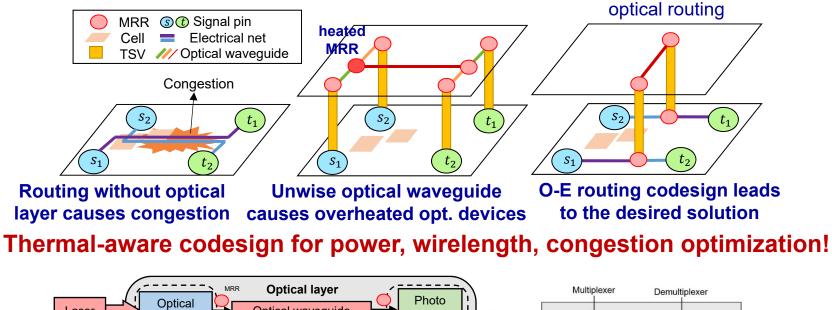

### **Optical-electrical Codesign**

- Lu, Chen, Hsu, and Chang, "Thermal-aware optical-electrical routing codesign for on-chip signal communications," DAC'22

- Generate global optical waveguides to optimize thermal impact, routing congestion, and wirelength

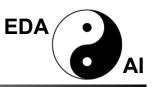

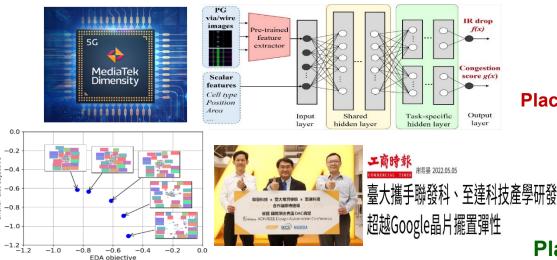

# Al for EDA & EDA for Al

- Al technologies reshape EDA

- Enhance EDA techniques with machine learning

### • EDA helps Al system designs

Optimize the design of CNN kernel structure

### AI for EDA

#### DAC'22: Macro Placement by MTK/MAXEDA/NTU

**EDA for AI** (chip design) kernel structure of a CNN accelerator

#### Placement by "leading" industry tool

Placement by NTU/MAXEDA tool (acquired by Synopsys in 2023) DAC'21

### Outline

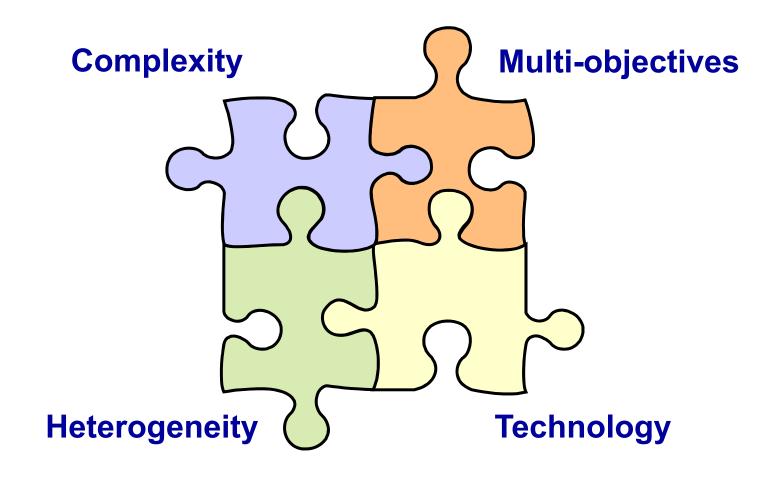

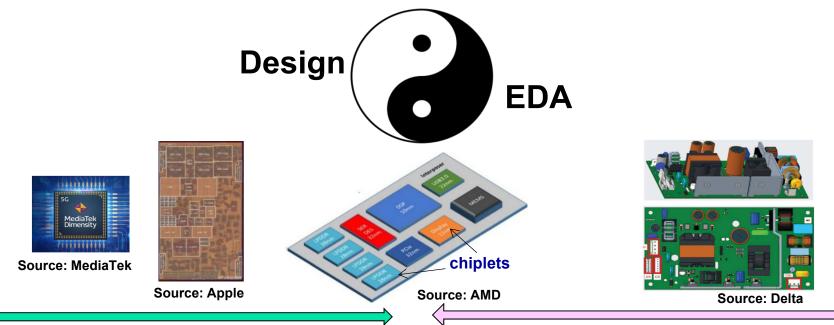

### **Modern Design/EDA Challenges**

### **Example 3D Placement Challenges**

- High complexity

- 100M objects + nets

#### Complexity

- Cross-physics constraints

- Multi-die technologies, warpage, thermal, etc.

Multi-objectives

- Mixed-cell-height, mixed-size placement

- 100K big macros with 100M small cells of multiple cell heights

#### Heterogeneity

### Emerging technologies

- AI, HI (bonding/integration TSV), etc.

- Technology

100M-cell + 100K-macro + 100M-net multi-die, multidomain mixedsize design

### **Culture Clash vs. Collaborative Mindset**

### chip to package

Large-scale, regular, homogeneous components w. uniform design rules

### board to package

Small-scale, irregular, heterogeneous components w. complex design rules

Chip Designers (Men) Are from Mars, Board Designers (Women) Are from Venus...

### Conclusions

Interposer EMIB InFO CoWoS SolC Chiplet Monolithic IC

- Multiple approaches to achieving the power/performance/area (PPA) holy grail

- Multiple complementary options to achieve the HI targets

- Need an ecosystem to achieve the ultimate PPA goal, where multi-physics domains need to be considered and EDA is essential

- Technology challenges will not limit our progress because imagination can bring us to the endless frontier!!

# Thank You!!

National Taiwan University