# **Unified 3D-IC Multi-Chiplet System Design Solution**

Thunder Lay, Software Engineering Group Director 03/12/2024

#### Outline

• 3D-IC Multi-Chiplet System Design Overview & Challenges

- Unified Multi-Chiplet System Design Solution

- Summary

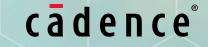

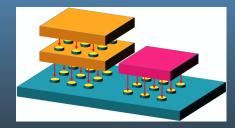

#### Unleashing the Power of Possibility by 3D-IC

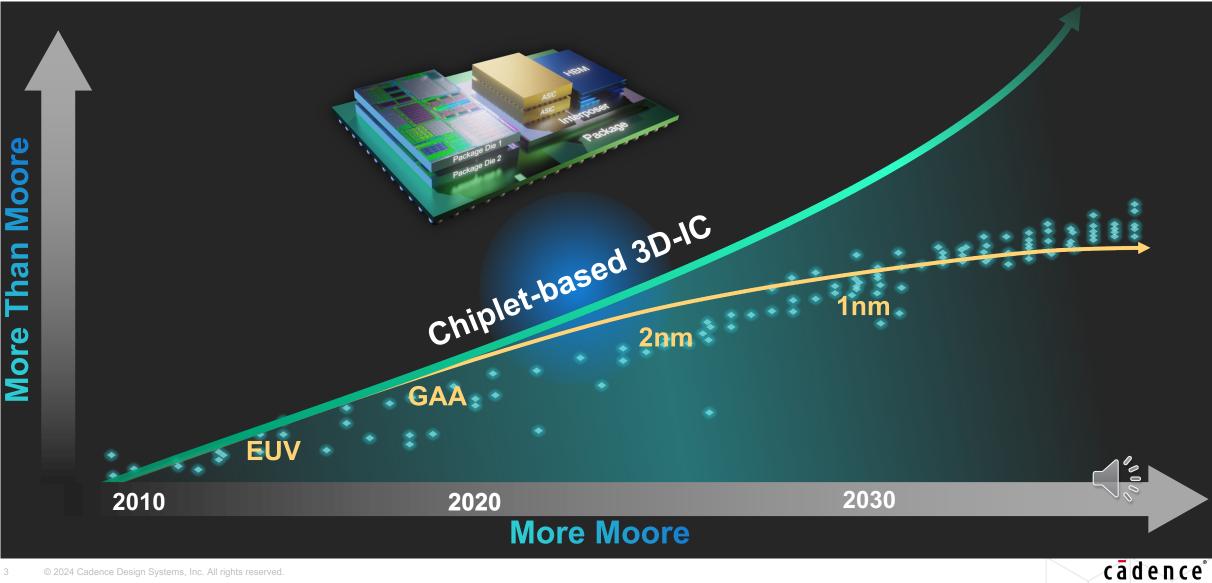

#### **3D-IC Development Challenges**

- 3D-IC heterogeneous design integration challenges

- System design challenges from planning, implementation to signoff

- Ecosystem challenges among Foundry/Customer/EDA

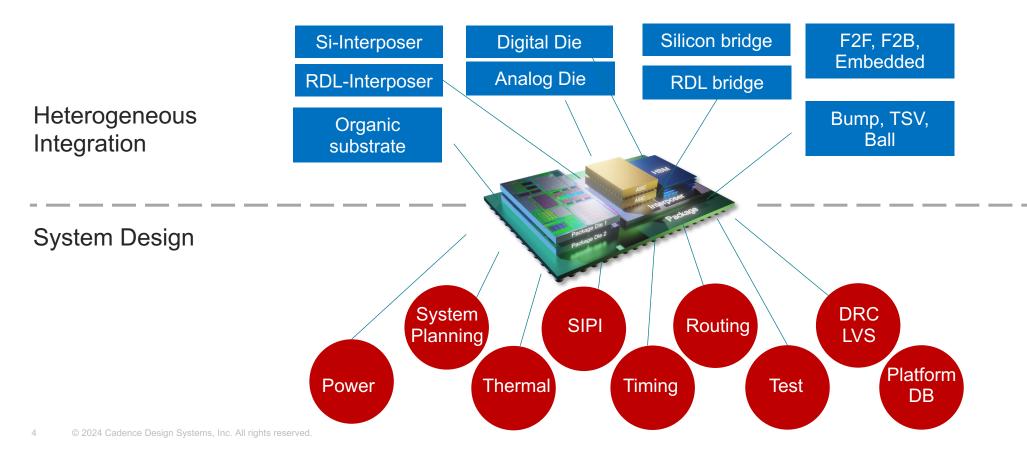

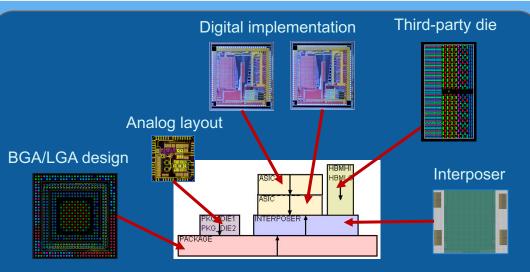

## **Overview 3D-IC Multi-Chiplet System Design flow**

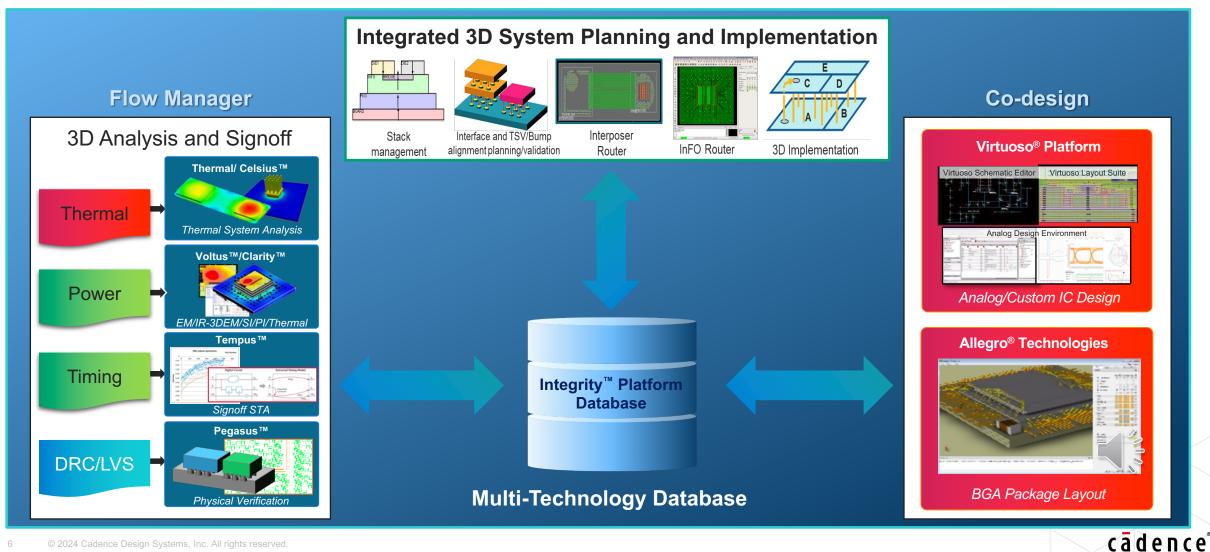

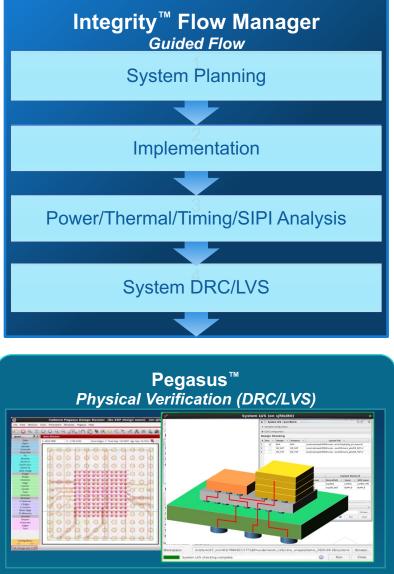

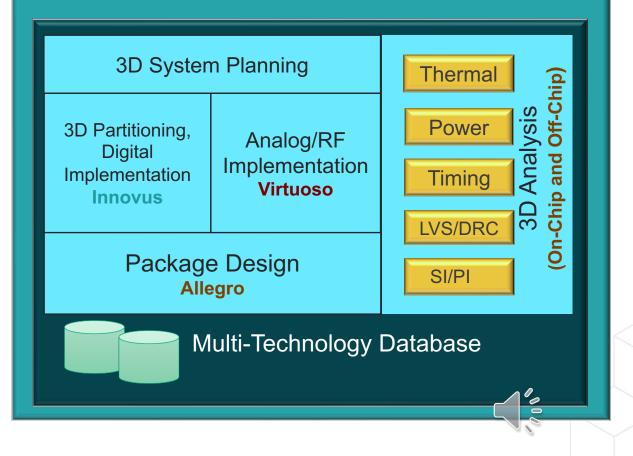

#### Unified 3D-IC Multi-Chiplet System Design Solution "Integrity 3D-IC"

Industry's first integrated, high-capacity 3D-IC platform that enables 3D design planning, implementation and system analysis in a single, unified cockpit

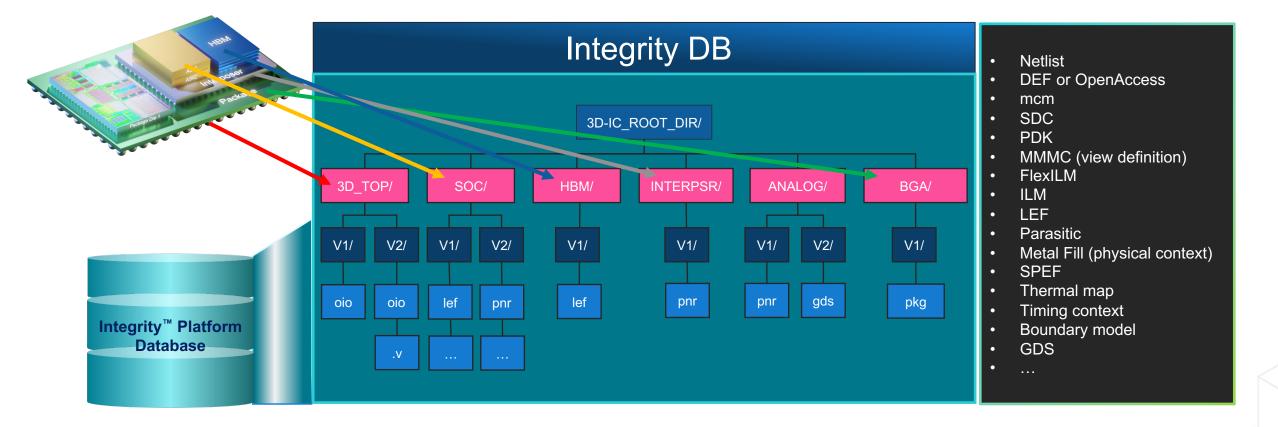

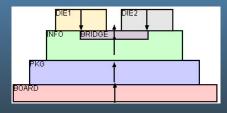

#### Platform Database for 3D Heterogeneous Integration Database innovation: Can handle <u>multiple technology nodes</u>

#### Hierarchical, Multi-Technology, Multi-Level, Multi-Model On-Demand DB

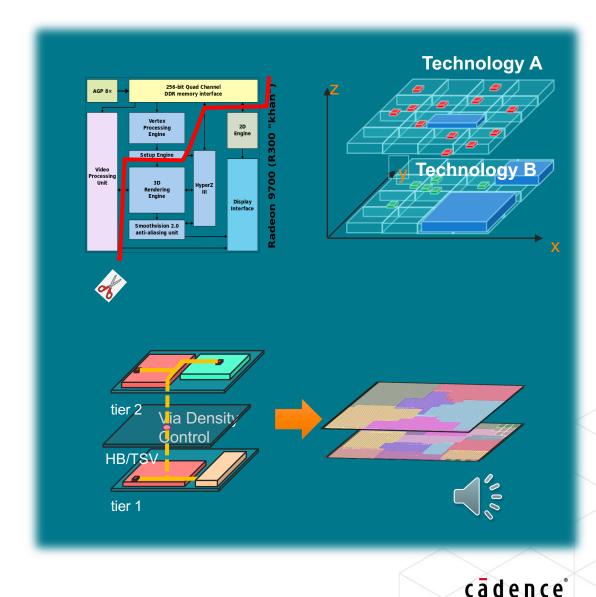

## 3D Native Partitioning and Floorplan Synthesis (3D-EFS)

- 3D IC block-level partitioning and placement.

- Considers 3D wire length, number of I/O ports/bumps/TSVs, different process node and timing

- Allow user to assign the die ID for hierarchical modules

- Per-die timing budgeting and bump assignment to enable per-die P&R or convert to pseudo 3D

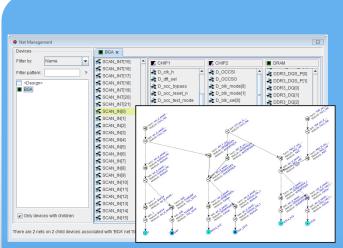

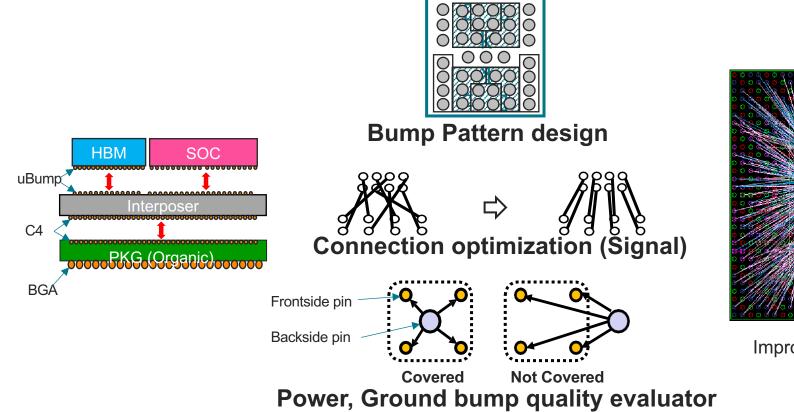

#### System Planning Capability Heterogeneous Integration Management & Optimization

Chip(let)-chip(let)-package-board signal-mapping

Hierarchical Planning and Optimization of System-level Design and Connectivity

Complete system-level view

Stack management

Interface alignment validation

System-level connectivity verification

Advanced bump/TSV planning

Bundle/bus-driven pin optimization

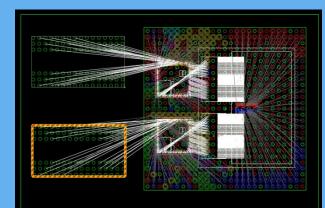

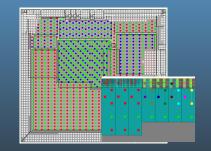

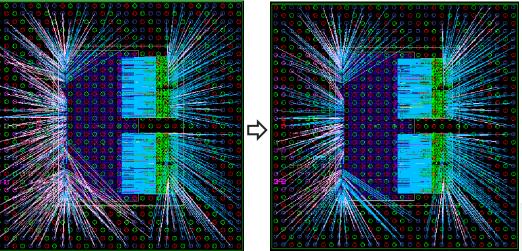

## Global Bump Planning, Optimization and Evaluation

- Bump/TSV/Ball assignment impacts 3D-IC System PPA.

- Connection optimization driven bump assignment improves routing congestion and wirelength.

Improve routing congestion compared with tapeoute design

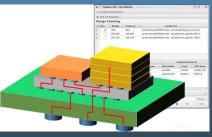

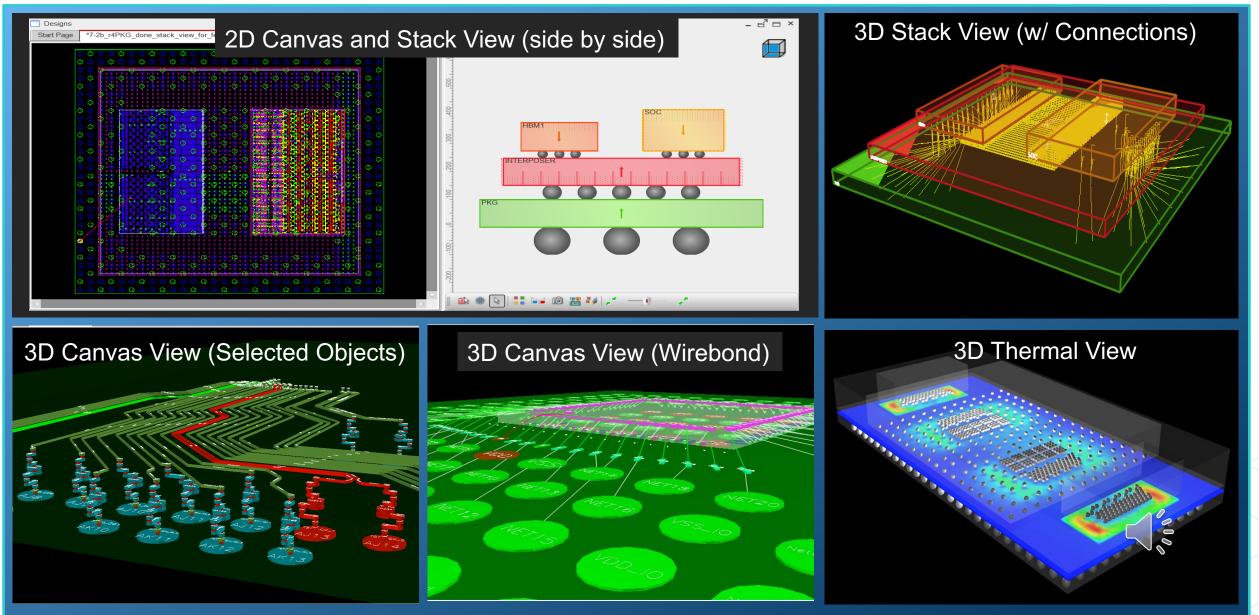

#### Multi-Chiplet Display in 2D/3D Viewing

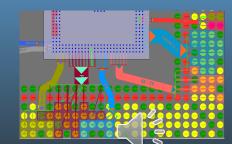

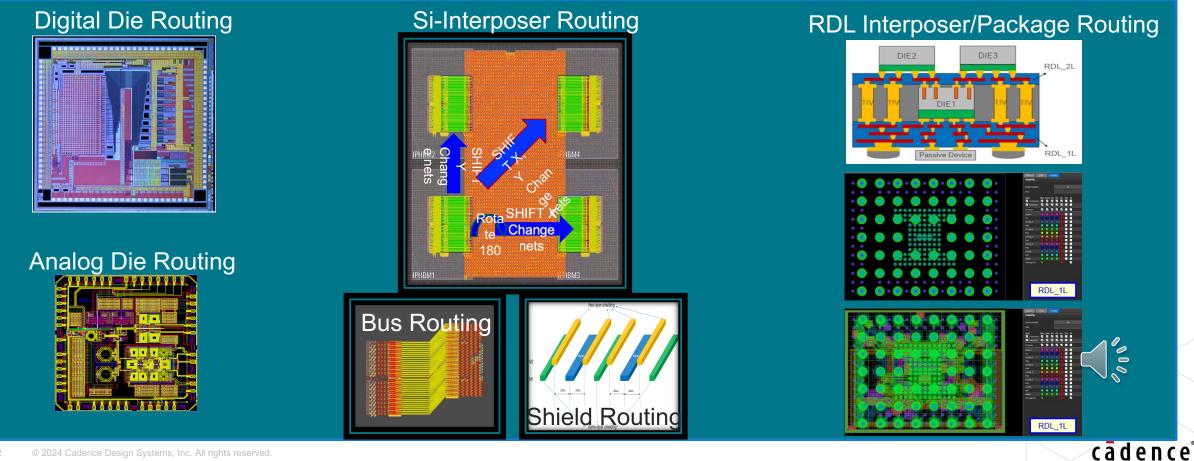

Implementation Technologies with Digital, Analog, RDL Routers

- Each type of design has different design constraints and routing style.

- Co-design integration with Digital, Analog, RDL routers.

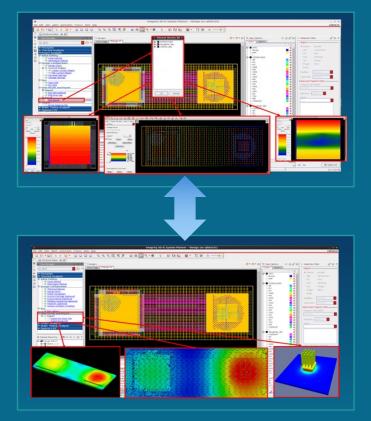

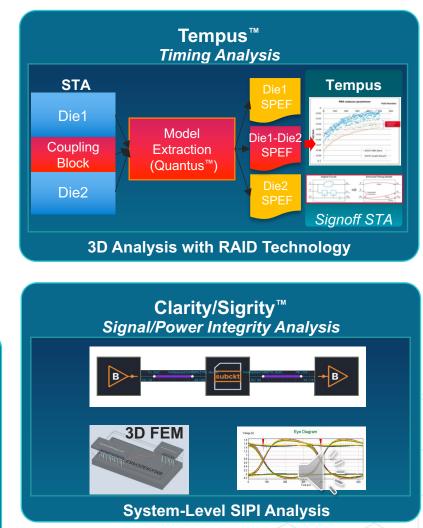

# Early System-Level Analysis and Signoff Flow

Voltus<sup>™</sup>/Celsius<sup>™</sup> Early Rail (Power and Thermal) Analysis

**System-Level Power and Thermal Analysis**

Inter-Die Connectivity Checking

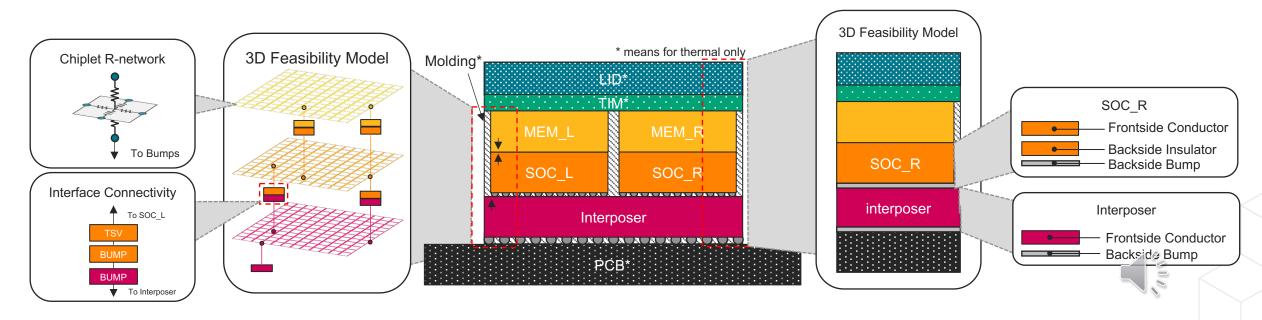

## IR/Thermal Early Feasibility Analysis

#### **IR-drop**

- Model the 3D design as a resistance network

- Abstract a chiplet's metal stack as a grided 2D resistance network

- Represent bumps/TSVs as resistors

- Chiplets are connected through bumps and TSVs

#### Thermal

- Model the 3D design as a layer-based stacking

- Condense chiplets into conductor or insulator layers

- Represent bump as a layer affixed to chiplets

- Model LID/TIM/PCB/Molding as a single structure of homogeneous properties

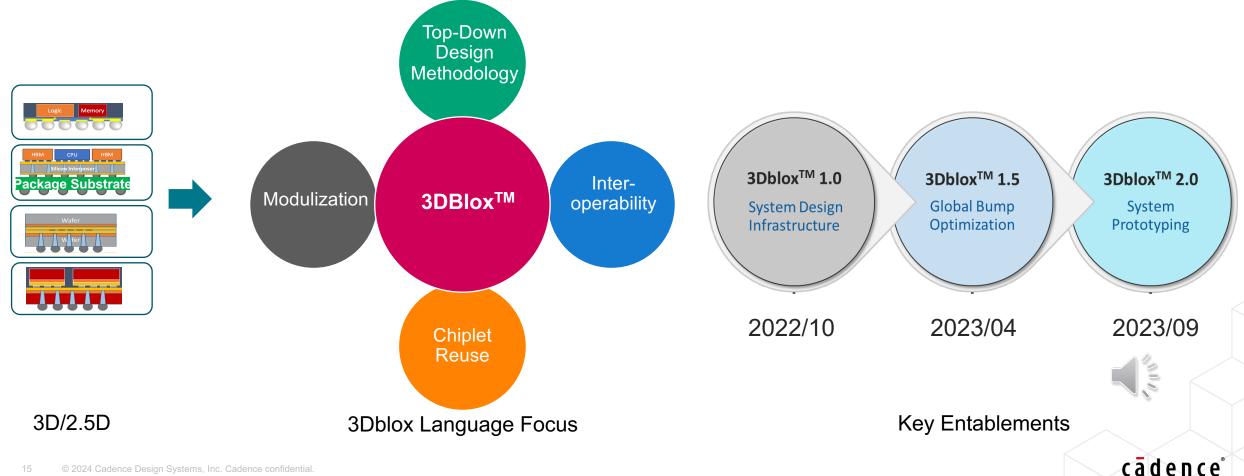

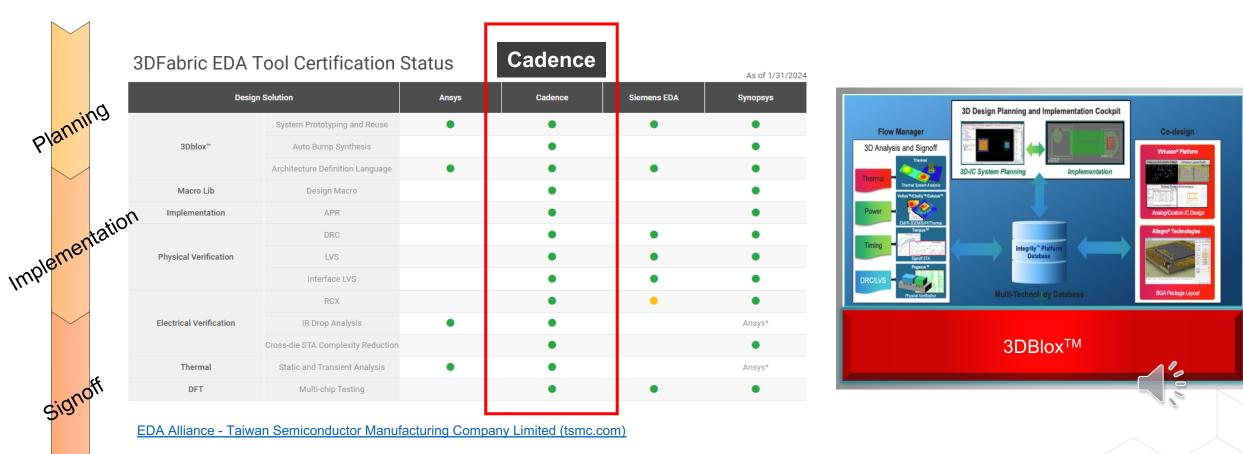

#### New 3D-IC Open Standard - 3Dblox<sup>™</sup> (https://3dblox.org/)

3Dblox Standard aims to streamline the 3D-IC package solutions in Planning, Implementation and Signoff.

## Close partnership with TSMC on 3Dblox<sup>TM</sup>

Integrity 3D-IC platform offers full flow solution

# Summary – Unified 3D-IC Multi-Chiplet System Design Solution

- System PPAC is goal

- Heterogenous integration capability

- A common platform DB

- Full system level multi-physics analysis technology for Thermal, Power, SI/PI and Physical Verification

- Ecosystem with leading foundries

#### Cadence Integrity 3D-IC Platform

# cādence®

© 2024 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <a href="https://www.cadence.com/go/trademarks">https://www.cadence.com/go/trademarks</a> are trademarks or registered trademarks or registered trademarks or registered trademarks or sevice marks found at <a href="https://www.cadence.com/go/trademarks">https://www.cadence.com/go/trademarks</a> are trademarks or registered trademarks or registered trademarks or sevice marks found at <a href="https://www.cadence.com/go/trademarks">https://www.cadence.com/go/trademarks</a> are trademarks or registered trademarks or sevice marks or registered trademarks or sevice marks of Accellera Systems Initiative Inc. All Arm products are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All Miles specifications are registered trademarks or trademarks of PCI-SIG. All other trademarks are the property of their respective owners.