# Novel Transformer Model Based Clustering Method for Standard Cell Design Automation

Chia-Tung (Mark) Ho, Ajay Chandna, David Guan, Alvin Ho, Minsoo Kim, Yaguang Li and Haoxing (Mark) Ren | ISPD 2024

### Introduction

- Novel Transformer Model Based Clustering Method

- Experimental Results

- Conclusion

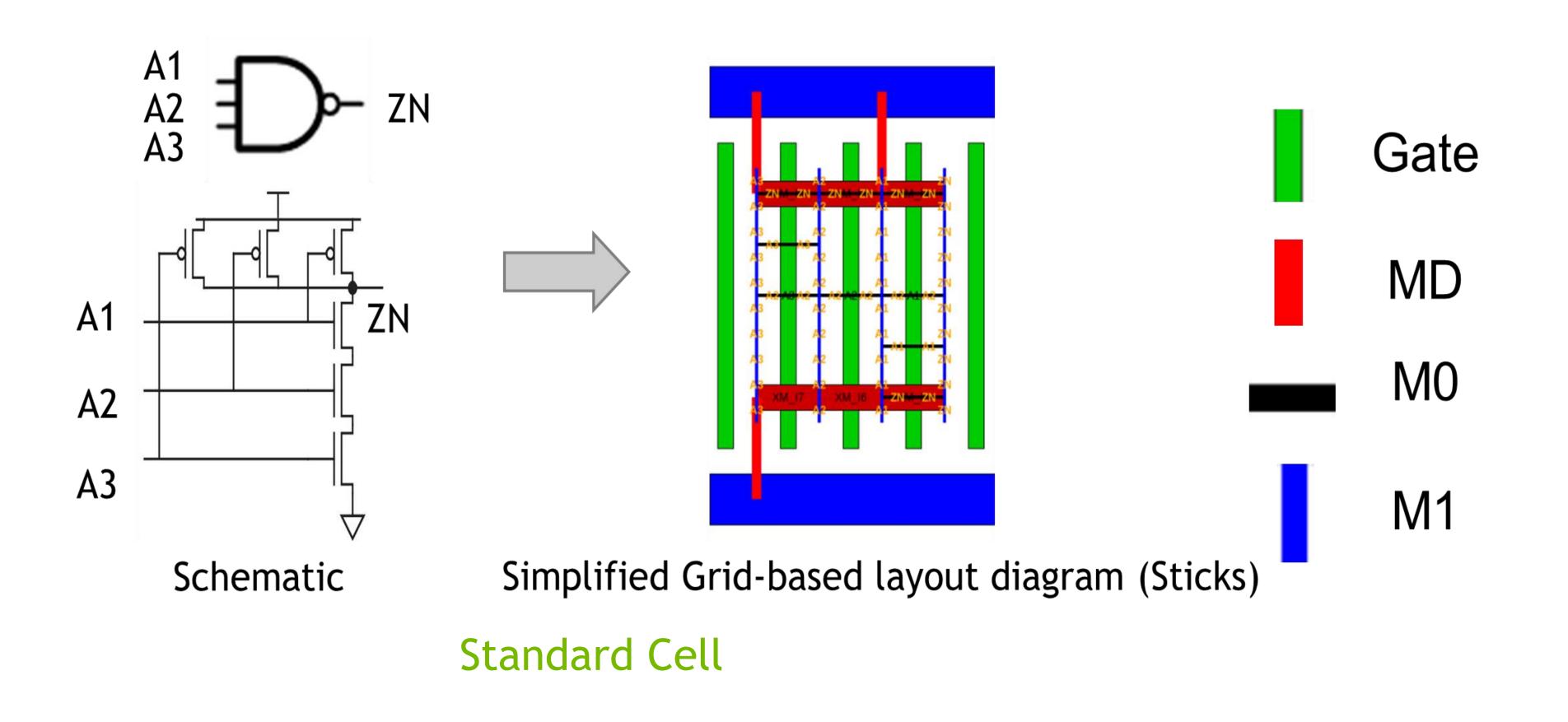

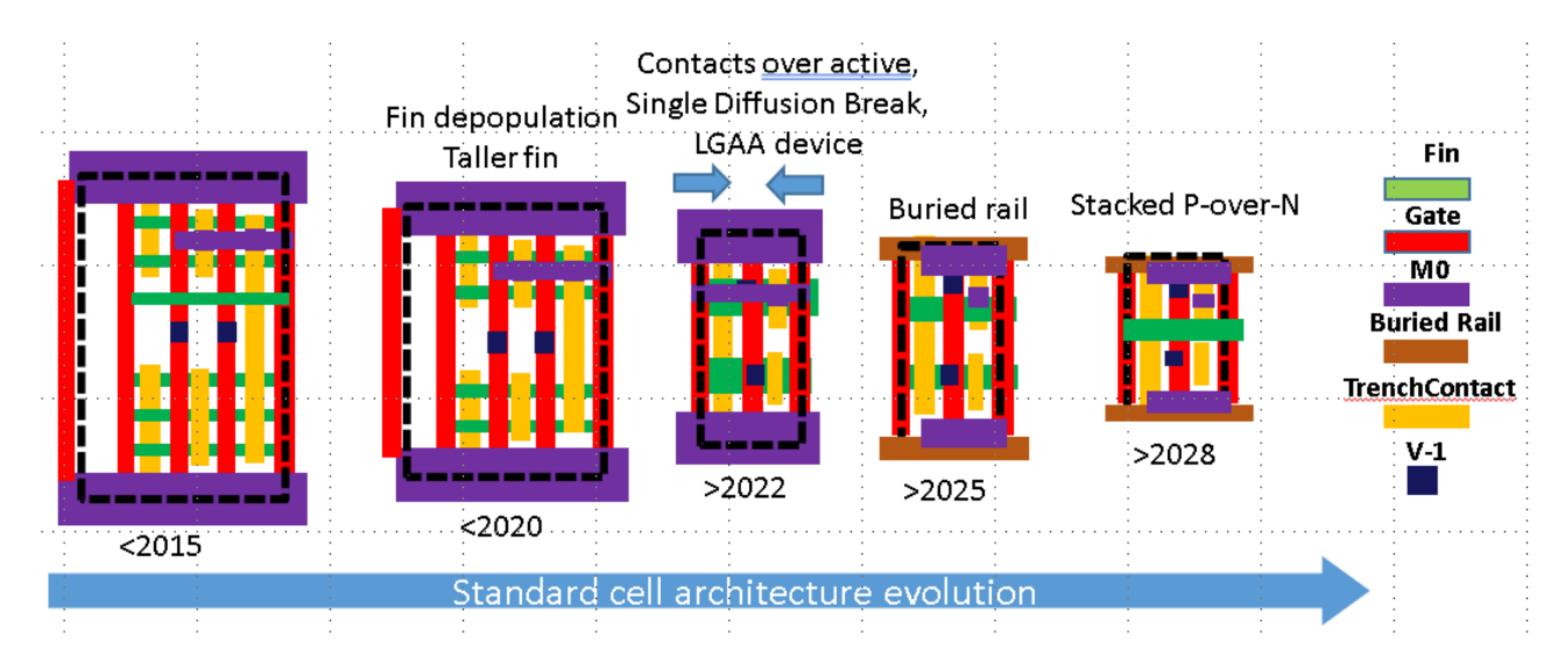

# **STANDARD CELL LAYOUT AUTOMATION**

- Standard Cells (STD) are building blocks of digital design layout: AND, NOR, Flip-Flop, Adder, etc • Months manual design turn around time per library to deliver competitive Power, Performance, and Area (PPA)

- Standard cell layout automation benefits NVCell (DAC2021, ISPD2023)

- Productivity: Fast turn around time

- Performance: Explore more design space

- Performance: More custom cell design

- Optimization: Design Technology Co-Optimization

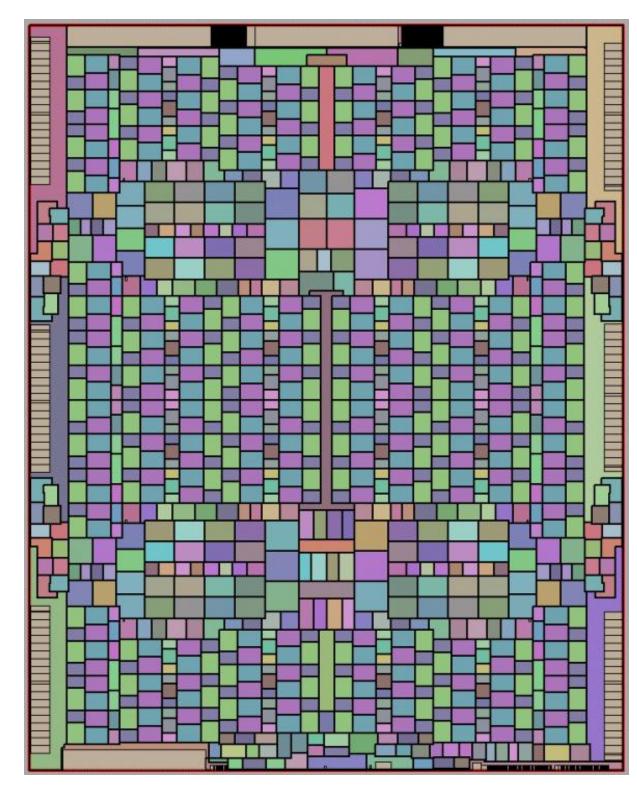

GA100 - 1.7B standard cells

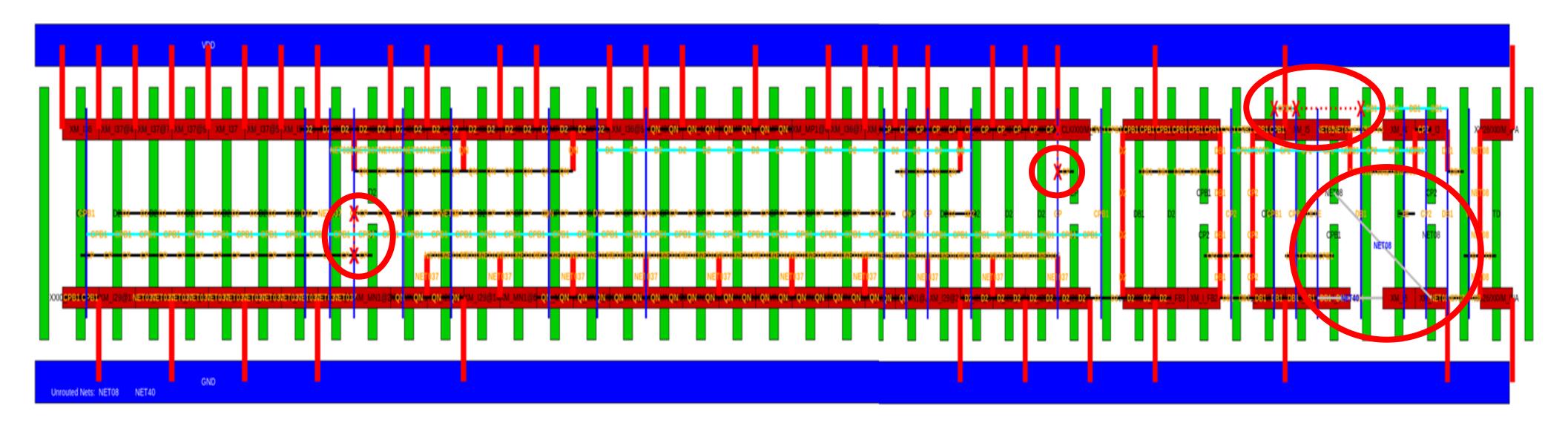

# CHALLENGES: STANDARD CELL LAYOUT AUTOMATION

- Standard cell layout automation challenges as advancing beyond 5nm • Limited in-cell routing resource: less routing tracks (i.e., 5 routing tracks) • Design rule complexity: Increasing number and complexity of design rules + strict patterning rules Scalability: > hundreds of transistors cell designs

- Better and Efficient standard cell layout automation framework

- Routability

- Scalability

- High-quality PPA

- How?

IRDS Roadmap 2022

Routability Challenges of a Latch Design in 5nm in stick format

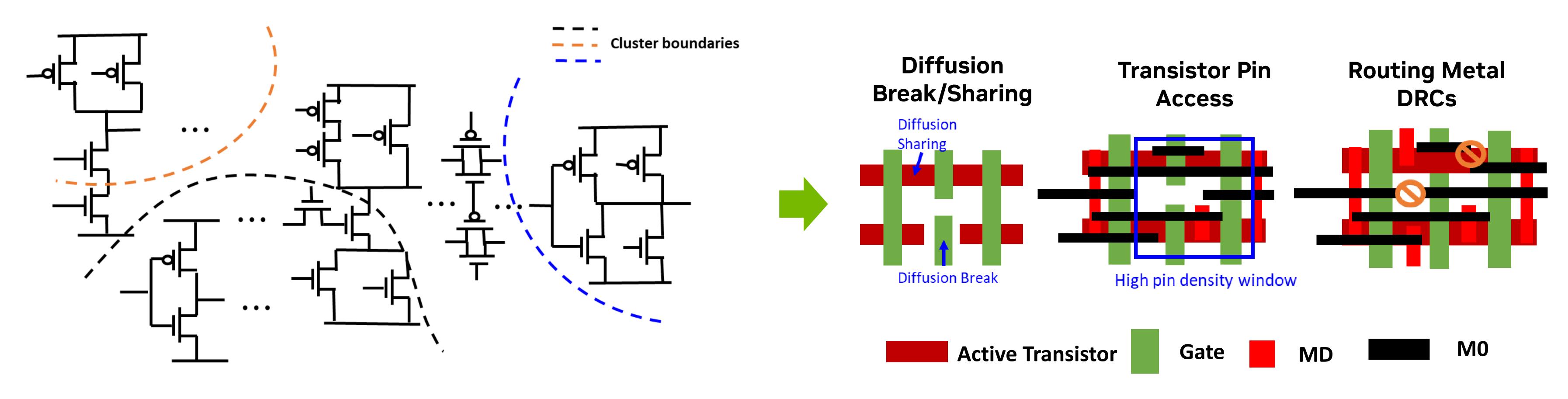

# LAYOUT-AWARE DEVICE CLUSTRING

- - Diffusion break/sharing

- Transistor pin access

- Routing metal DRCs

### Novel transformer model-based clustering methodology

- Reduce complexity

- Narrow down searching space

- Assist finding routable + optimal layouts faster

• High quality device clustering should consider transistor layout characteristics

- Introduction

- Novel Transformer Model Based Clustering Method

- Experimental Results

- Conclusion

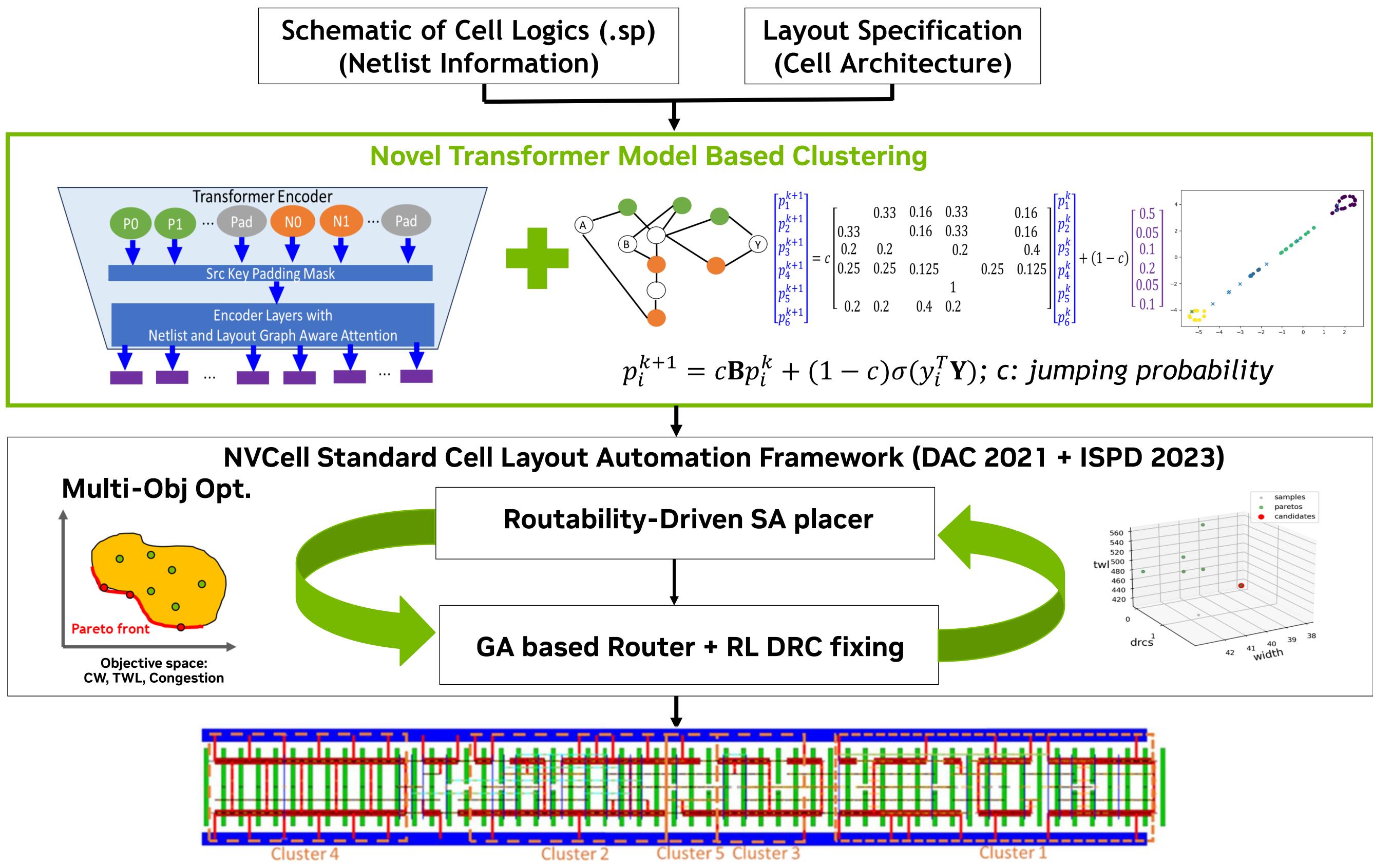

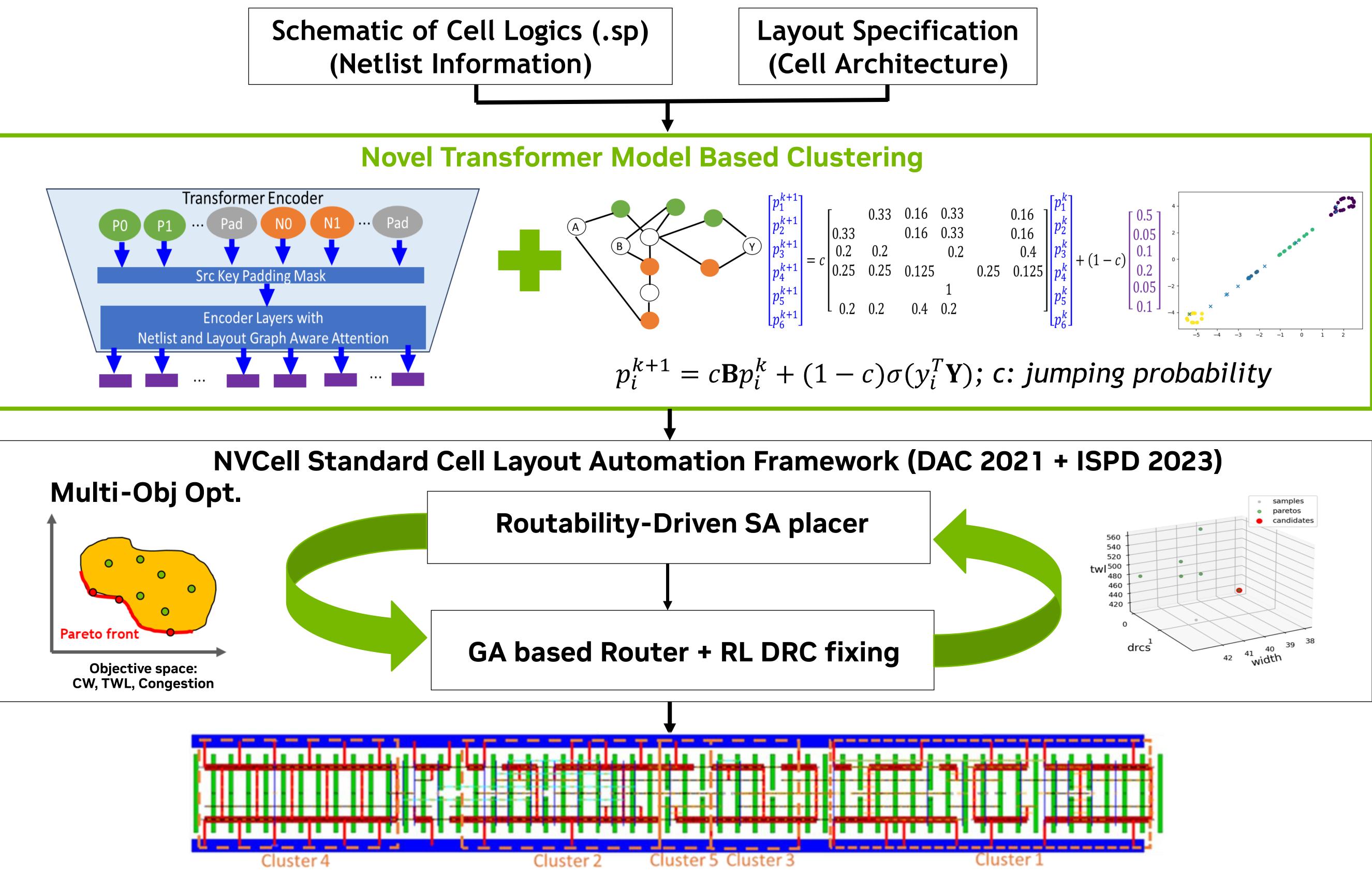

# NOVEL TRANSFORMER MODEL BASED CLUSTERING METHOD

Framework Overview

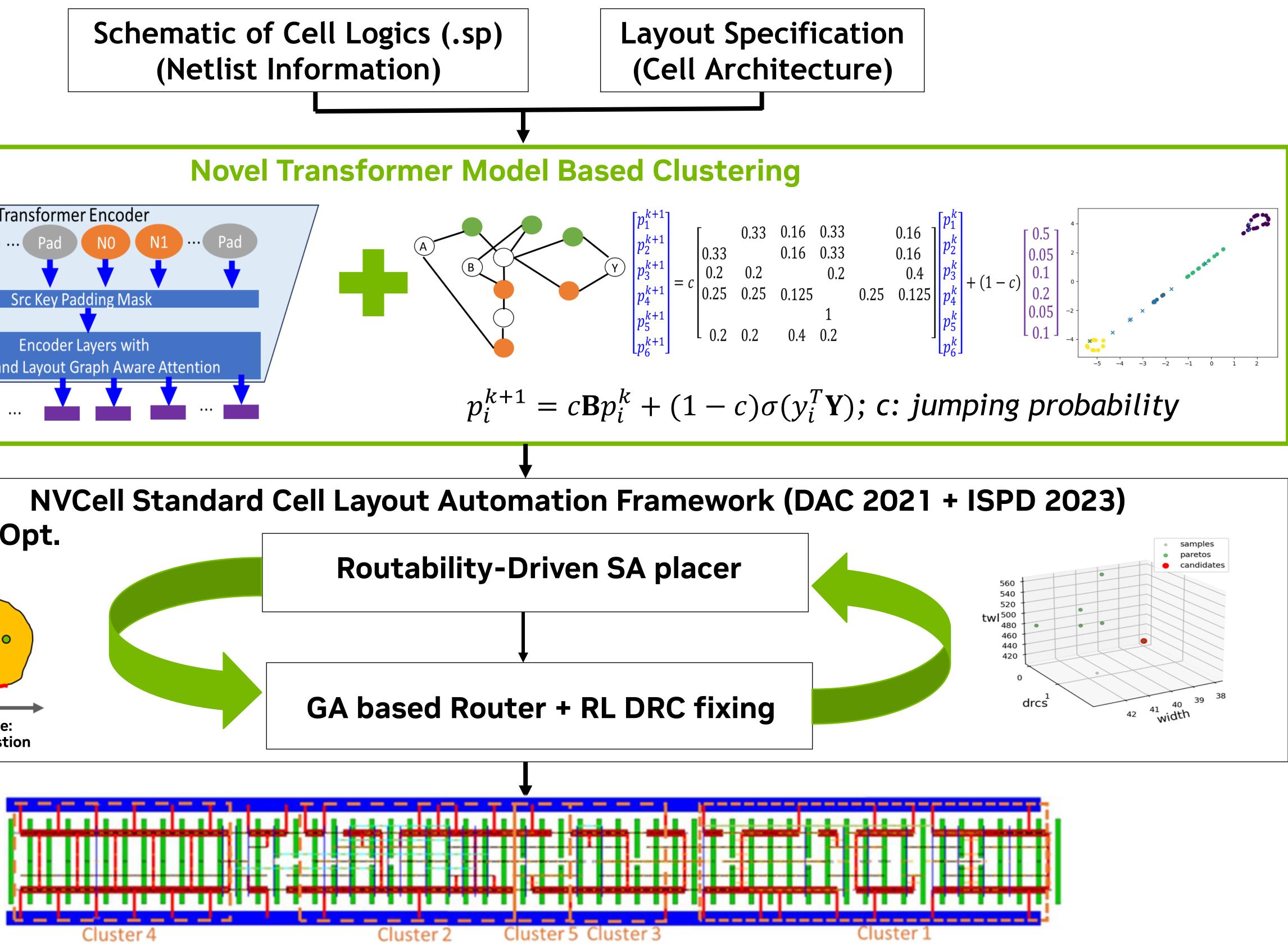

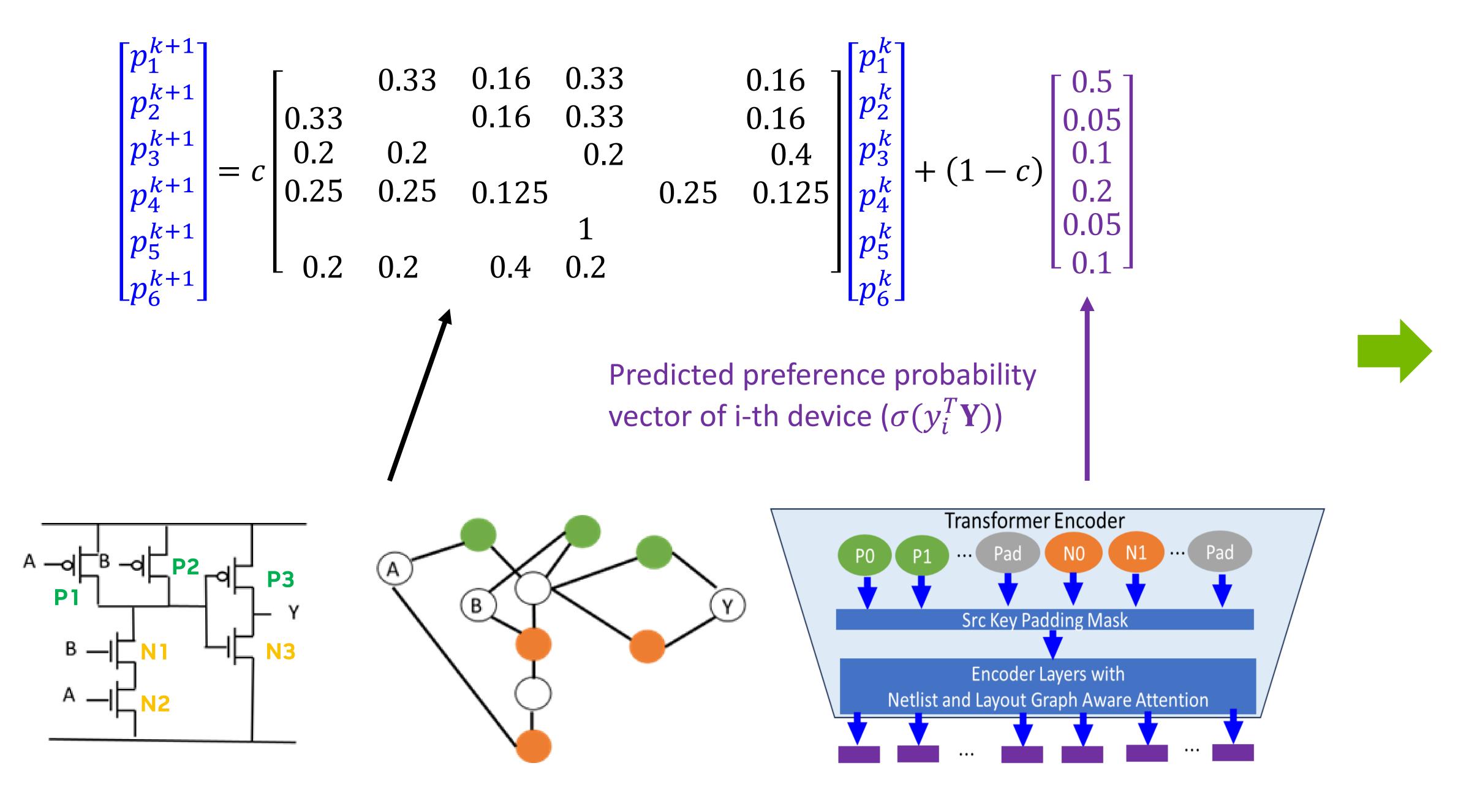

# **TRANSFORMER ENCODER STRUCTURE**

$$= \sum_{v} \left( -\sum_{u \in N(v)} \log \left( \sigma(y_{v}^{T} y_{u}) \right) - \sum_{k \sim rand} \log \left( \sigma(-y_{v}^{T} y_{k}) \right) \right)$$

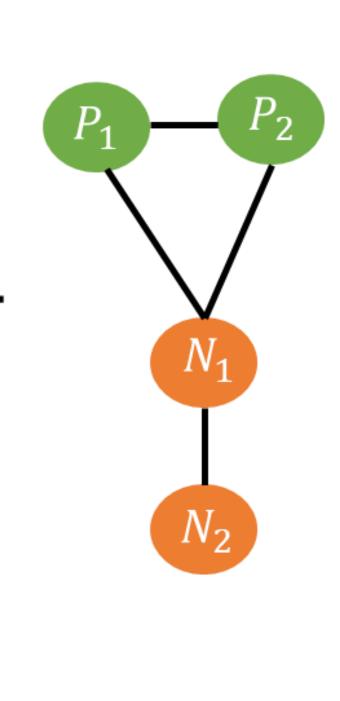

- Goal: Learn the relationship between device pairs in the layout graph

- Netlist logic graph: Topology is from spice netlist

- Nodes: Nets, devices, and pins

- **Edges: Connections**

- Layout graph: Neighbor grids are all connected

- Column: gate terminal

- Row: PFET, NFET

- Unsupervised learning from LVS/DRC layouts

- Global receptive field + Netlist Structure + Device placement relation

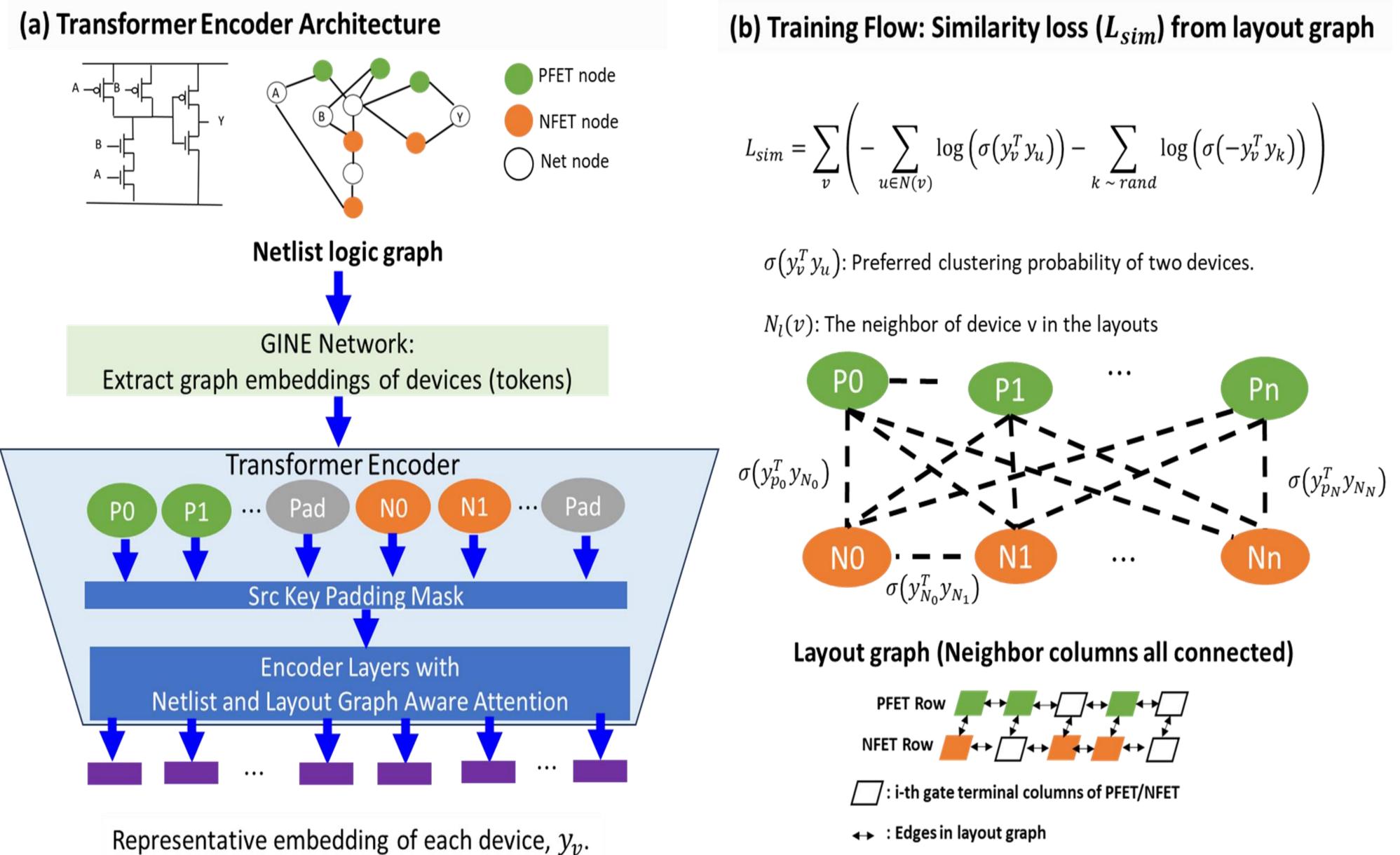

# **NETLIST & LAYOUT GRAPH MULTI-HEAD ATTENTION**

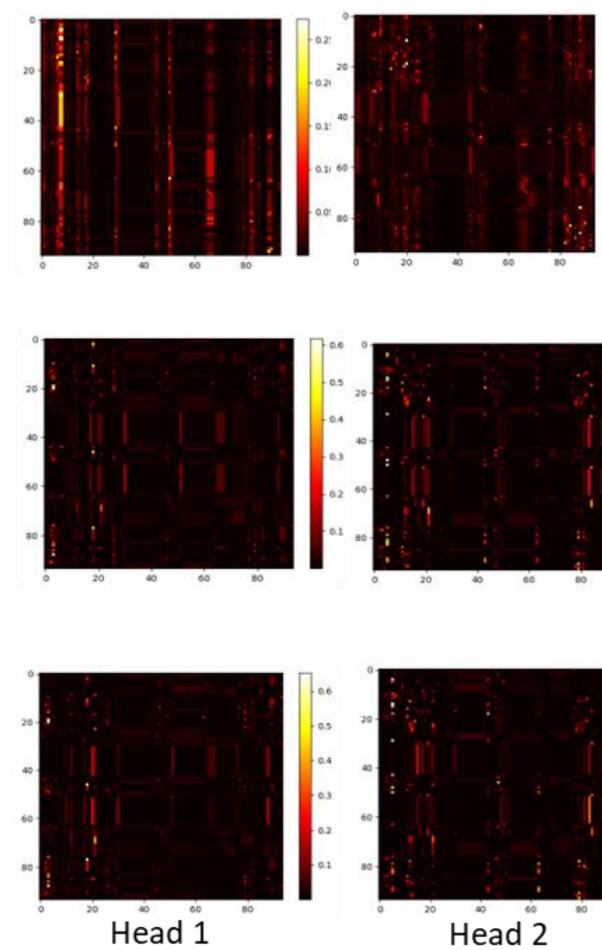

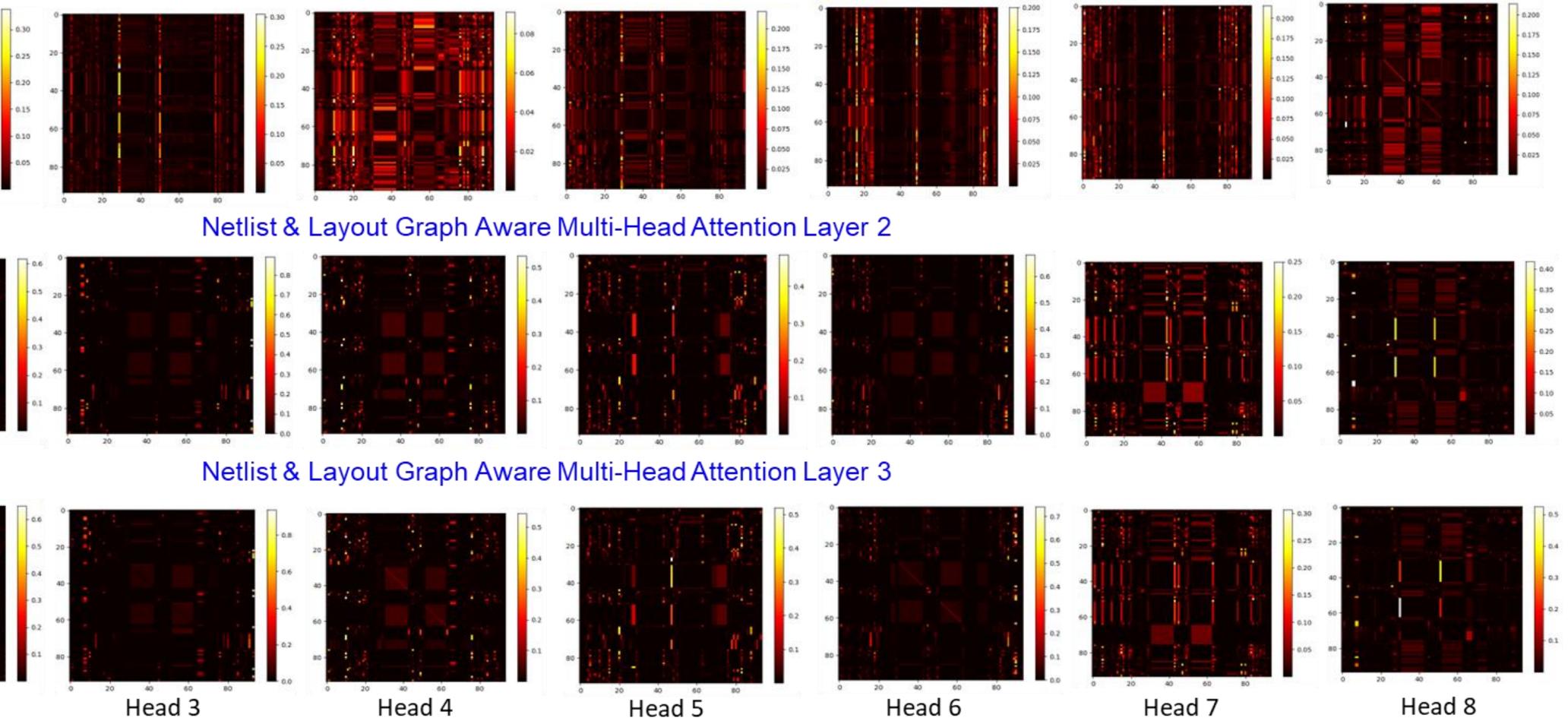

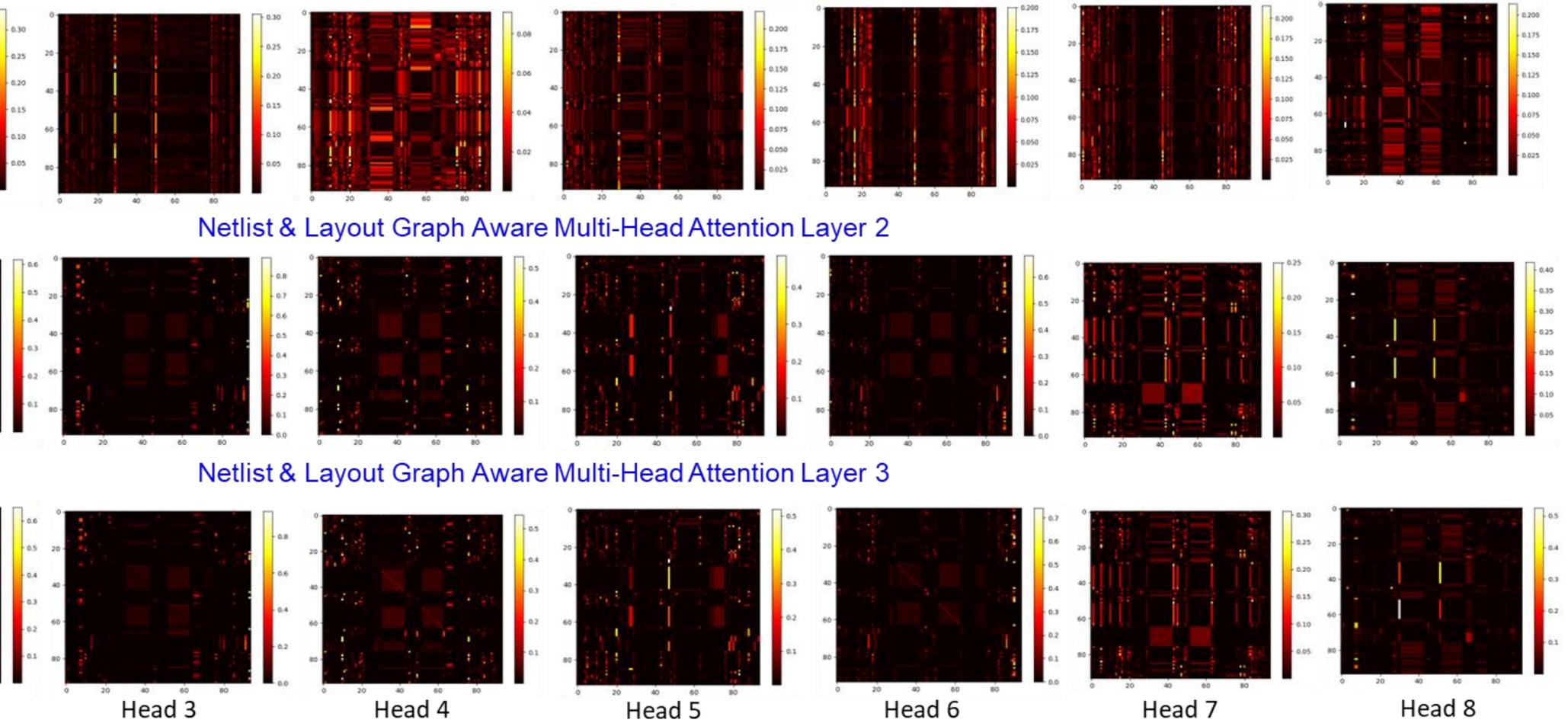

- connect.

$a_{v,u} = \frac{(h_v \mathbf{W}_{\mathbf{Q}})(h_u \mathbf{W}_{\mathbf{K}})^T}{\sqrt{d}} + b_{\phi(v,u)} + b_{\kappa(v,u)}$   $\begin{array}{c} \mathbf{Spatial} \\ \mathbf{Spatial} \\ \mathbf{P'} \end{array}$

Relation Attn bias

Placement Attn bias

Spatial Relation bias: shortest path distance between devices in the netlist logic graph

Device Placement bias: device layout characteristics, such as diffusion sharing, vertical gate/diffusion

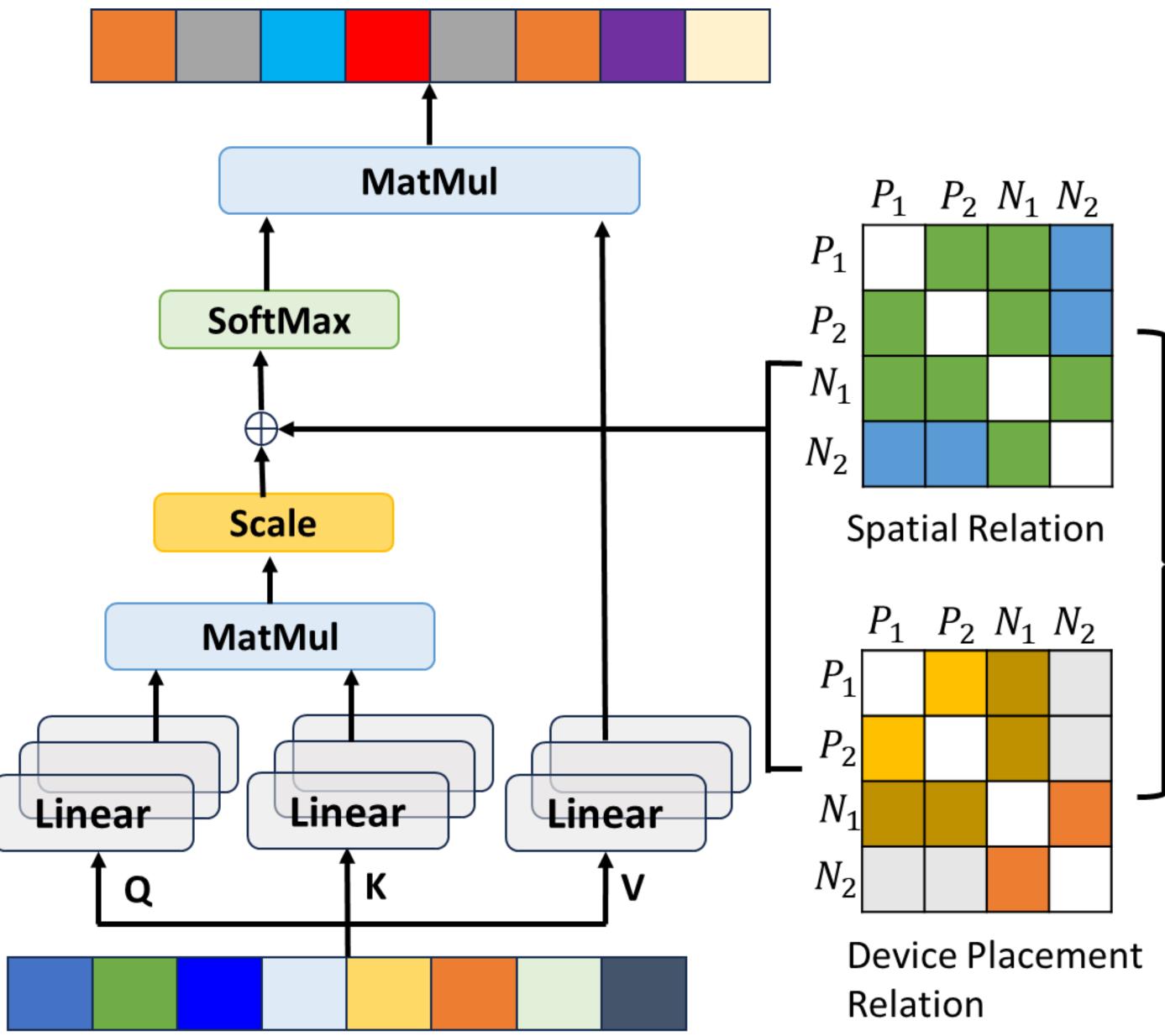

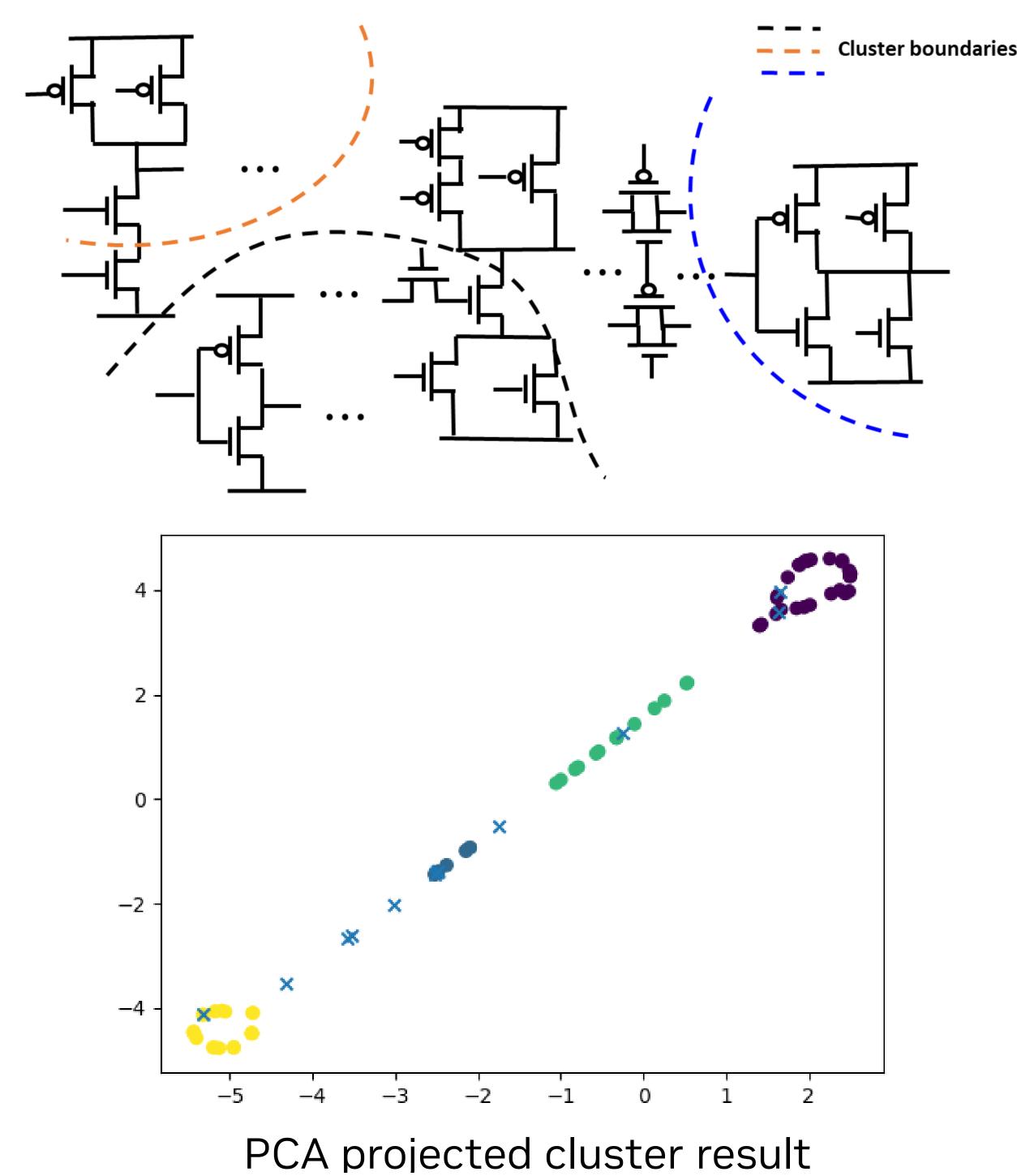

## NETLIST & LAYOUT AWARE PERSONALIZED PAGE RANK VECTOR CLUSTERING

### For each device, calculate personalized page rank vector $p_i^{k+1} = c \mathbf{B} p_i^k + (1 - c) \sigma(y_i^T \mathbf{Y})$ ; c: jumping probability

**DBScan Clustering from**  $p_i$

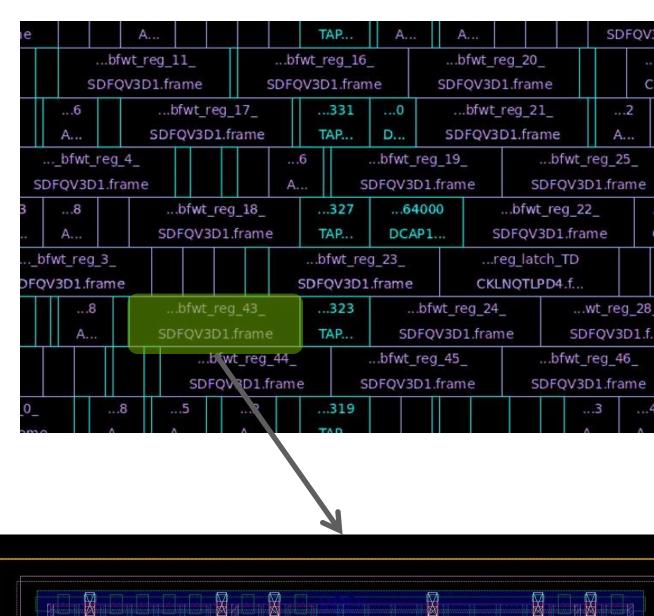

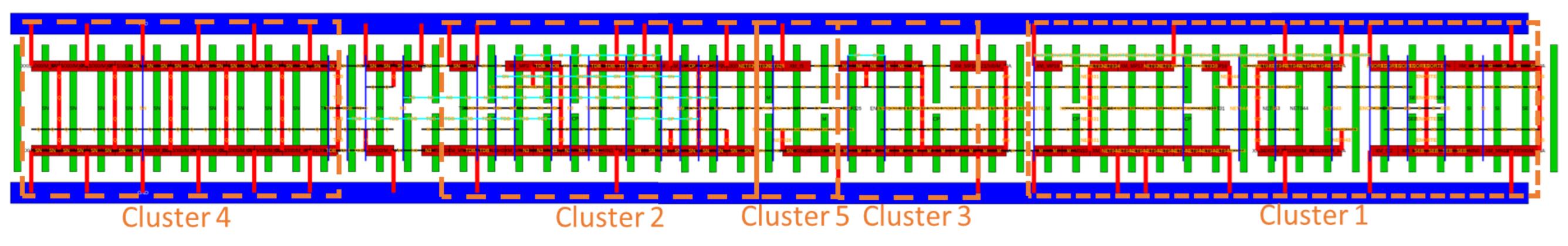

### **GENERATED LVS/DRC LAYOUT AFTER CLUSTERING** Generated LVS/DRC Clean Latch Design (~ 100 devices)

Head 1

### Manual Cell Width = 58 / Generated Cell Width = 56 TWL = 671

### Netlist & Layout Graph Aware Multi-Head Attention Layer 1

- Introduction

- Novel Transformer Model Based Clustering Method

- Experimental Results

- Conclusion

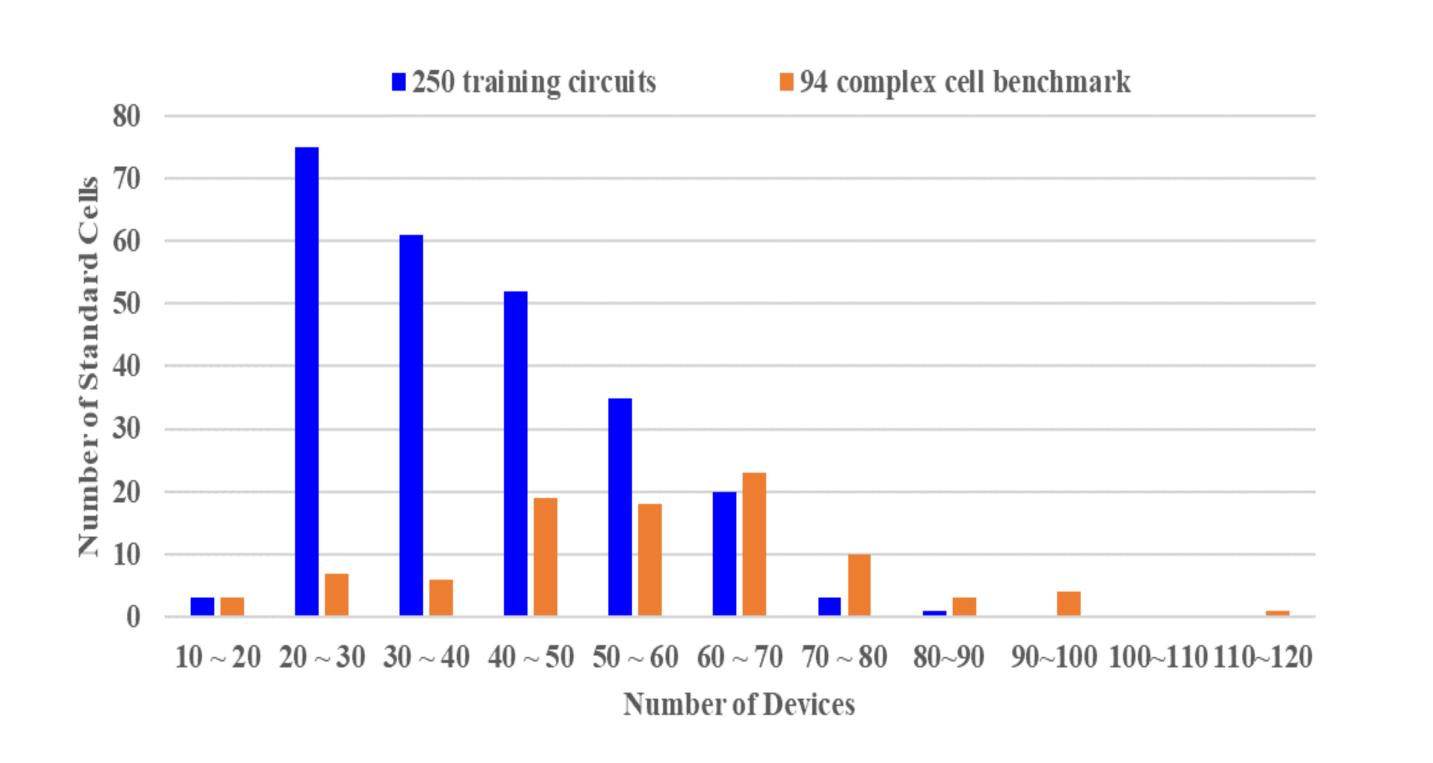

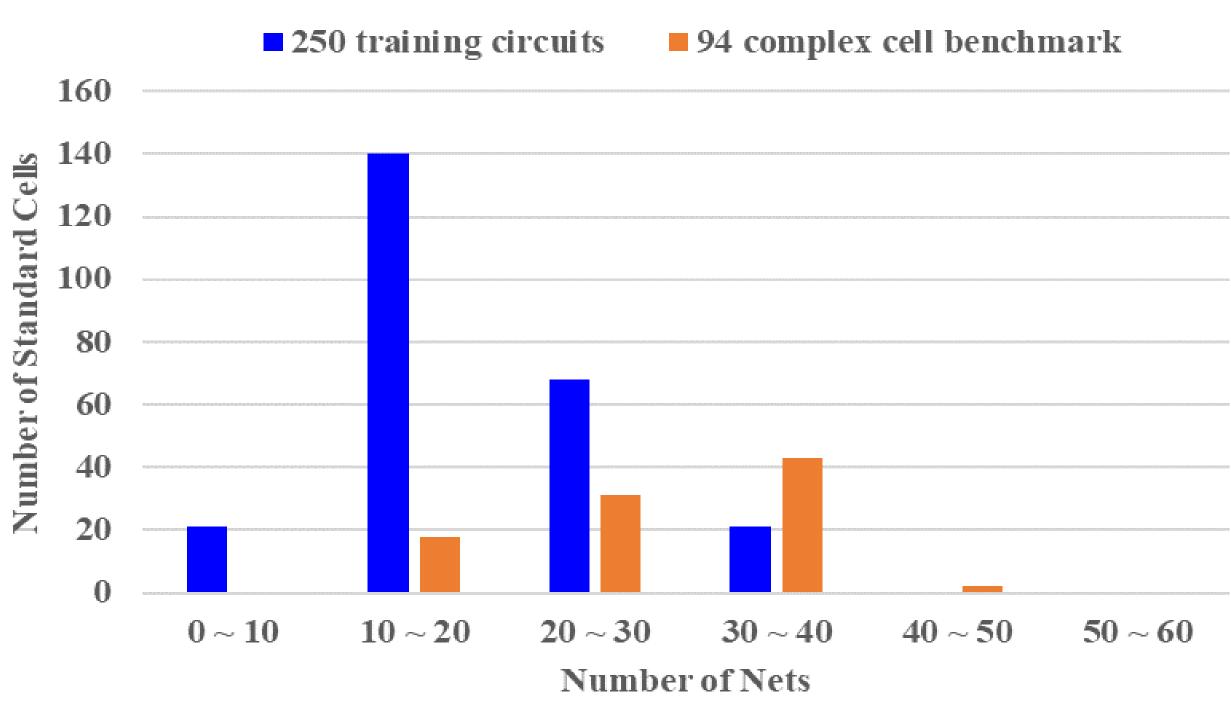

- Training 250 training circuits set in 5nm library

- Apply to larger and more complex circuits

- Apply to different technology nodes

- <u>Experiment I:</u> Clustering Quality Study

- <u>Experiment II</u>: Results of 5nm industrial library

- 94 complex cell benchmark + Entire cell library

- <u>Experiment III</u>: Results of 3nm (without retraining the model)

## **Experimental Setup**

- lacksquare

- ullet

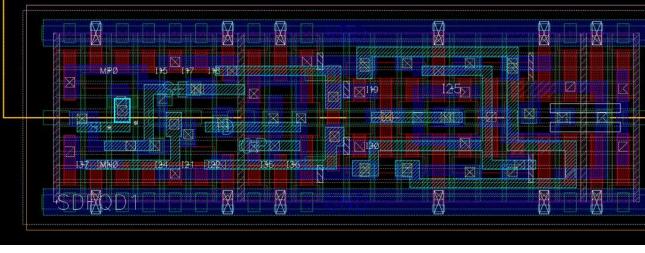

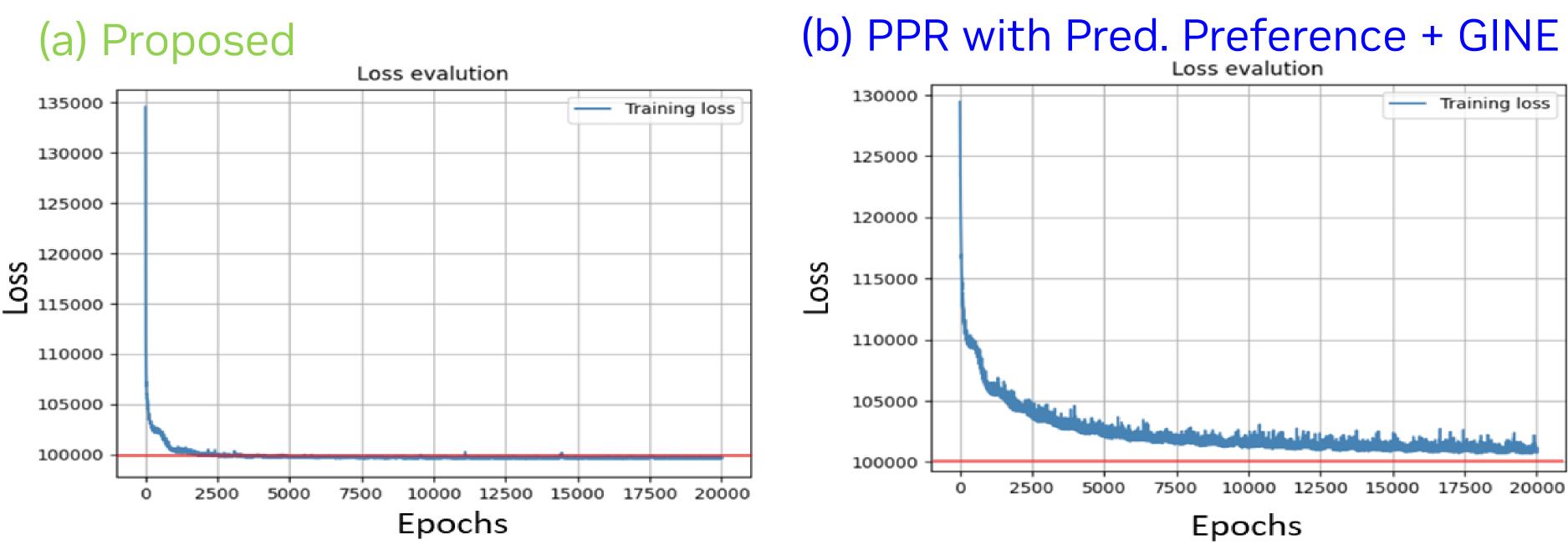

| Rep. Node Vectors | Model                        | Avg. Silhouette | Impr. (%) |

|-------------------|------------------------------|-----------------|-----------|

| Pred. Preference  | GINE                         | 0.21            | 200%      |

|                   | Transformer based            | 0.42            | 50%       |

| PPR with Pred.    | N/A                          | 0.22            | 186%      |

| Preference        | GINE                         | 0.37            | 70%       |

|                   | Transformer based (proposed) | 0.63            | —         |

## **Clustering Quality Study**

Quality of DBScan clustering method with Different Models and Representative Node Vectors (Rep. Node Vectors) Silhouette score (Larger is better): clustering result and the actual LVS/DRC clean layout placement

Silhouette score =  $\frac{(b-a)}{\max(a,b)}$ ; a = mean intraclass distance; b = mean nearest cluster distance

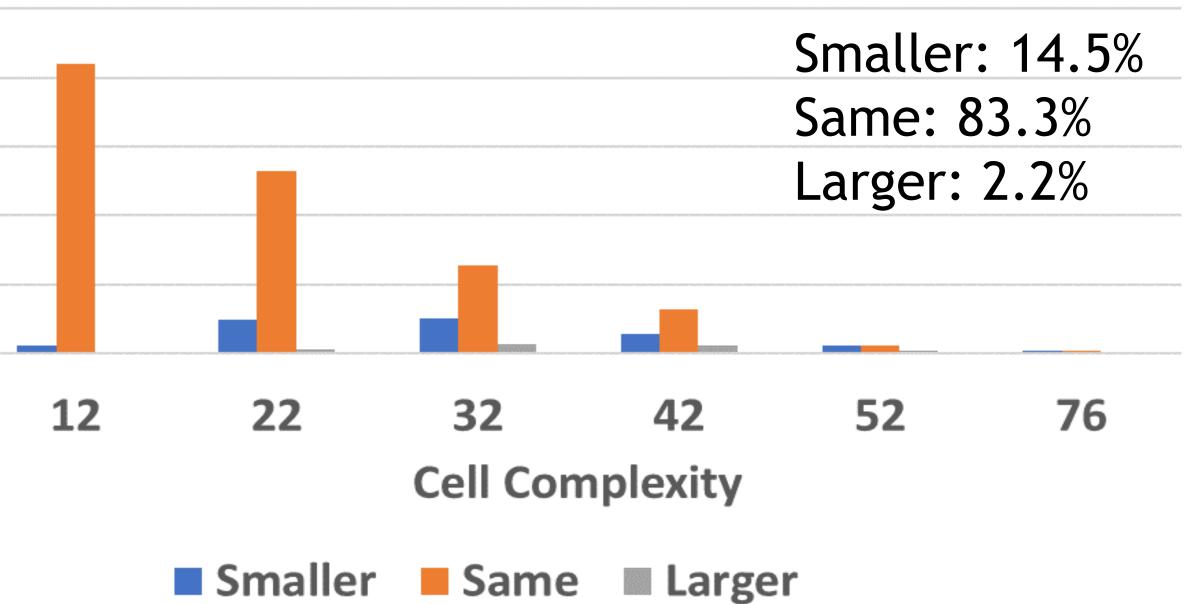

|             | Success  | Cell \  | Cell Width Comparison |        |  |

|-------------|----------|---------|-----------------------|--------|--|

|             | Rate (%) | Smaller | Same                  | Larger |  |

| NVCell      | 0%       | N/A     | N/A                   | N/A    |  |

| (DAC 2021)  |          |         |                       |        |  |

| NVCell2     | 87.2%    | 22.3%   | 37.2%                 | 27.7%  |  |

| (ISPD 2023) |          |         |                       |        |  |

| Proposed    | 100%     | 29.8%   | 58.5%                 | 11.7%  |  |

On a difficult routing benchmark (94 cells)

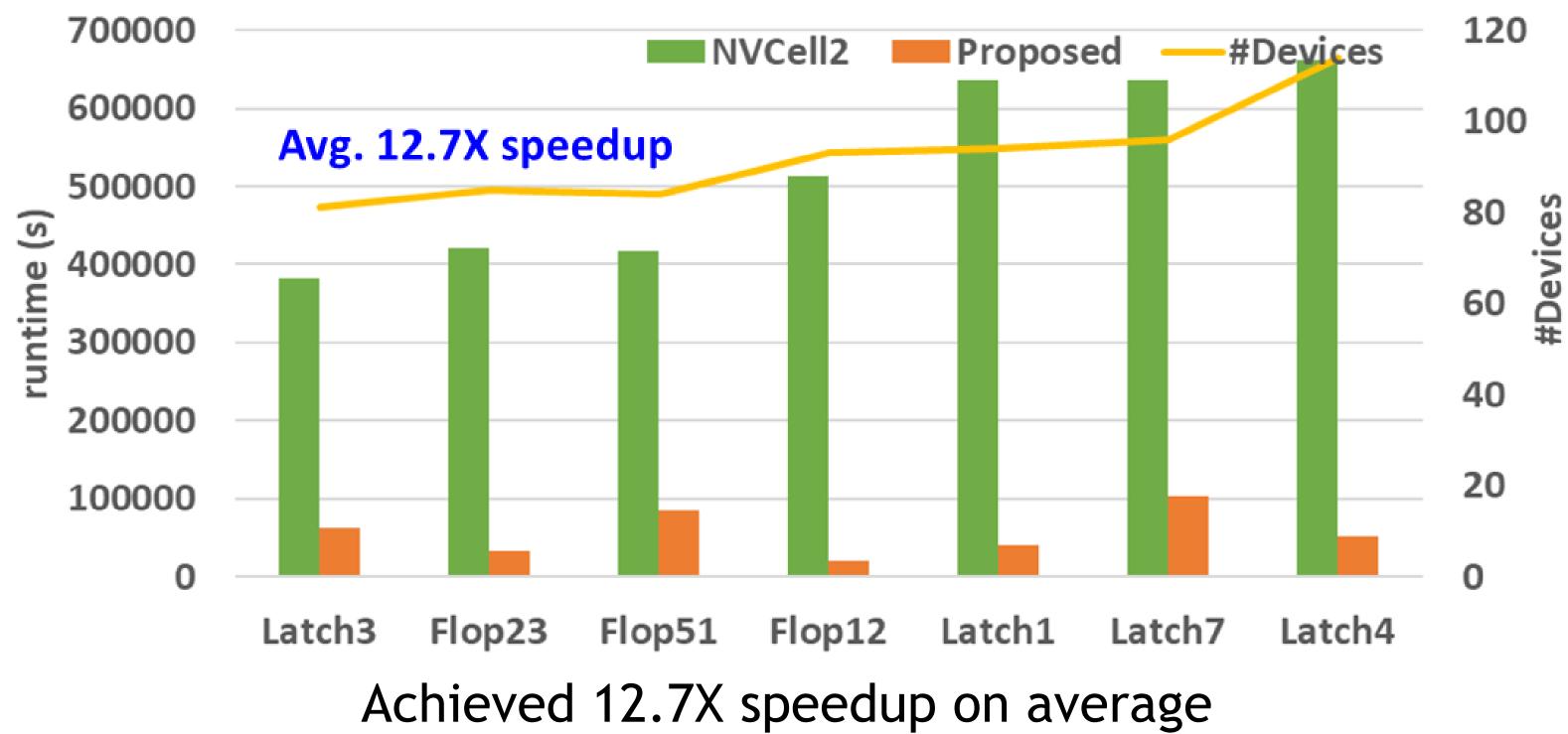

## **RESULTS of 5nm**

|      | 500 | 10000000000                             |

|------|-----|-----------------------------------------|

|      | 400 |                                         |

| slls | 300 | 100000000000000000000000000000000000000 |

| Ű#   | 200 |                                         |

|      | 100 |                                         |

|      | 0   | Server Server                           |

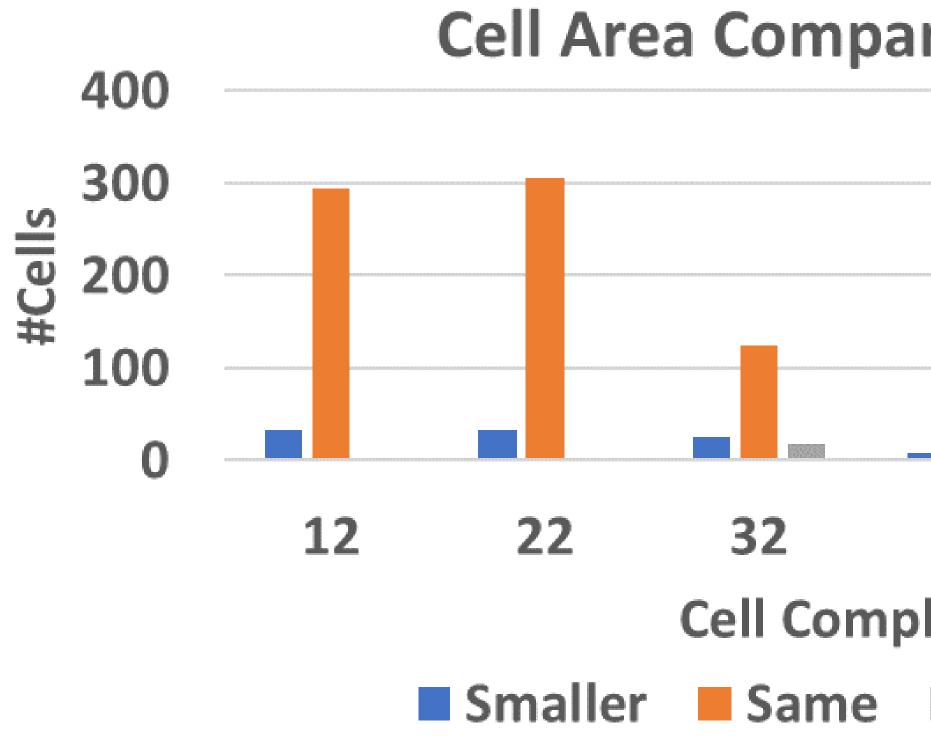

### **Cell Area Comparison**

| Success  | Cell Width Comparison |       |        |  |

|----------|-----------------------|-------|--------|--|

| Rate (%) | Smaller               | Same  | Larger |  |

| 91.2%    | 11.8%                 | 77.6% | 1.8%   |  |

| 98.8%    | 13.7%                 | 80.1% | 4.3%   |  |

| 100%     | 14.5%                 | 83.3% | 2.2%   |  |

On entire cell library (1078 Cells)

### **5 Routing Tracks Cell Archite**

|          | Success  | Cell Width Comparison |       |        |

|----------|----------|-----------------------|-------|--------|

|          | Rate (%) | Smaller               | Same  | Larger |

| Proposed | 100%     | 11.4%                 | 81.7% | 4.4%   |

Total Cell: 938 Cells

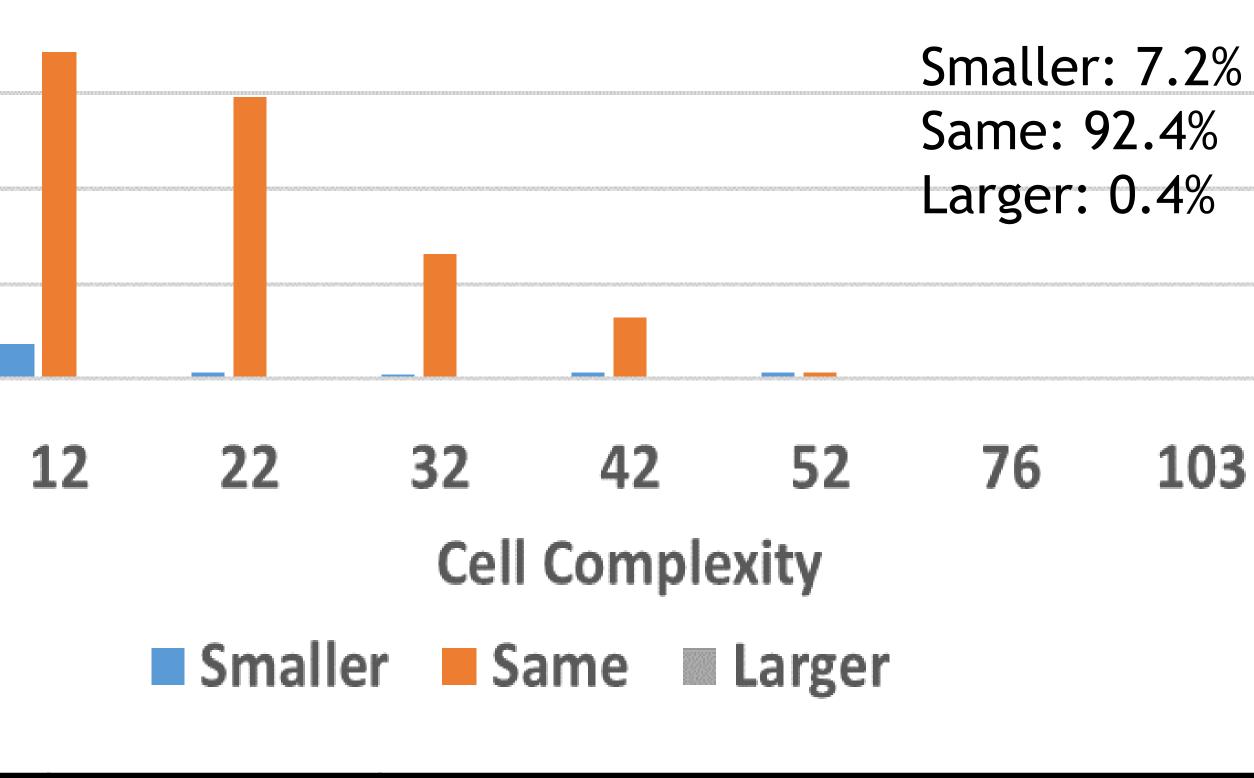

### **RESULTS of 3nm** Without Retraining Model

| ecture (93 | 38 Cell    | s)        |                   | 4              |

|------------|------------|-----------|-------------------|----------------|

| irison     |            |           | 200               | 00110011001100 |

|            | Small      | er: 11.4% | 200               |                |

|            |            | : 81.7%   | ് 150             |                |

|            | Large      | r: 4.4%   | ୍ଥ<br>ଅପ୍ତ<br>100 |                |

|            |            |           | <sup>#</sup> 50   |                |

|            | 0001010000 |           | 0                 |                |

| 42         | 52         | 76        |                   |                |

| olexity    |            |           |                   |                |

| -          |            |           |                   |                |

| Larger     |            |           |                   |                |

### **Routing Tracks Cell Architecture (458 Cells)**

### **Cell Area Comparison**

| Success  | Cell Width Comparison |       |      |  |

|----------|-----------------------|-------|------|--|

| Rate (%) | Smaller               | Same  | Larg |  |

| 100%     | 7.2%                  | 92.4% | 0.4% |  |

Total Cell: 458

- Introduction

- Novel Transformer Model Based Clustering Method

- Experimental Results

- Conclusion

- and area

- 100% success rate for 5nm

- 14.5% smaller cell width + 83.3% same cell width

- Transferable to different technology nodes

- Future works:

- PPA-driven standard cell layout automation

- Cluster constraint debugging and optimization for PPA

# CONCLUSIONS

• Proposed Novel Transformer Model Based Clustering Method successfully improves the success rate, performance,

Avg. 12.7X speedup on cells with > 80 devices than previous work

• Competitive PPA result: Power impr. up to 12%, Delay impr. up to 8%, and Area impr. up to 14.29%