# X-Volt: Joint Tuning of Driver Strengths and Supply Voltages Against Power Side-Channel Attacks

Saideep Sreekumar, Mohammed Ashraf, Mohammed Nabeel, Ozgur Sinanoglu,

Johann Knechtel

International Symposium on Physical Design – Online, March 29, 2023

Sreekumar, et al., "X-Volt: Joint Tuning of Driver Strengths and Supply Voltages Against Power Side-Channel Attacks," ISPD' 23, March 29

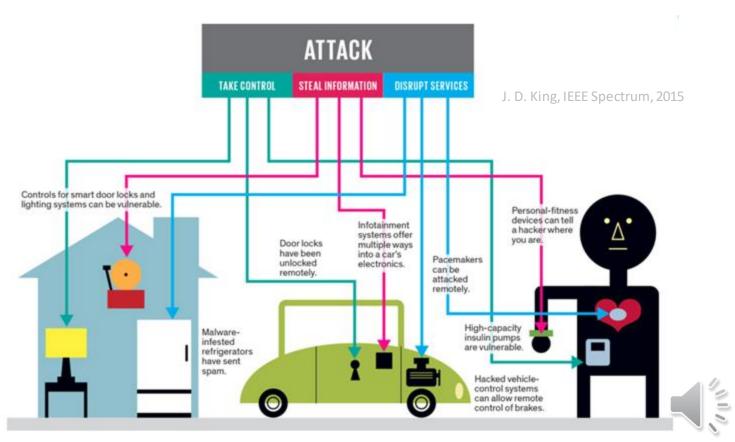

## Data and Computation at Risk – Right at the Hardware

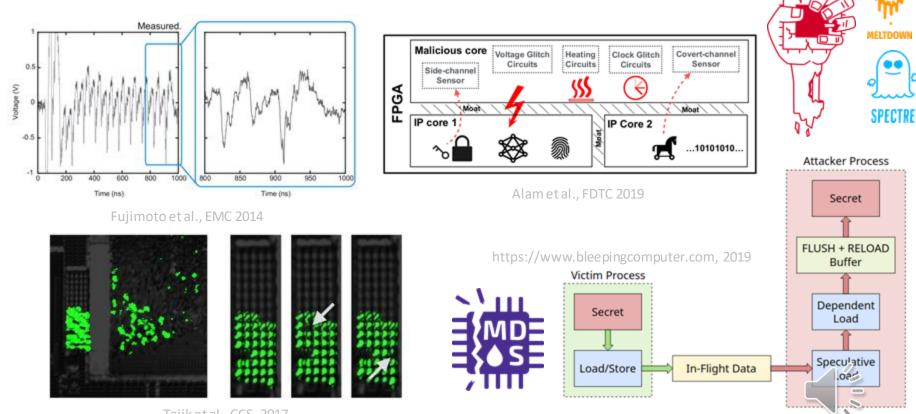

Tajik et al., CCS, 2017

Hardware Security Basics Motivation Methodology Setup Results Conclusion

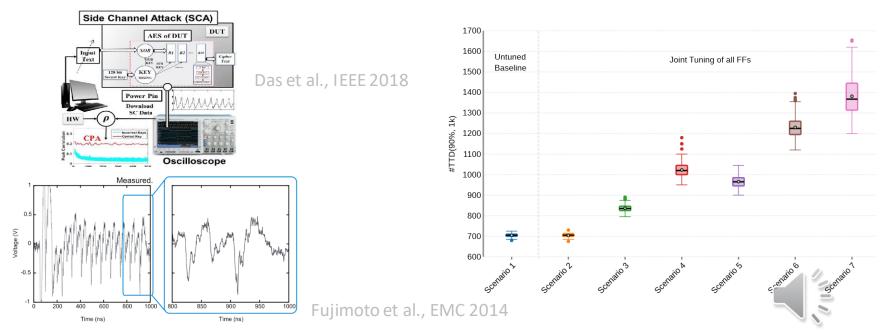

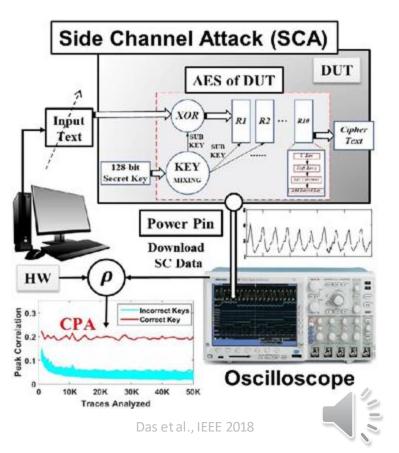

### Side-Channel Attacks (SCA)

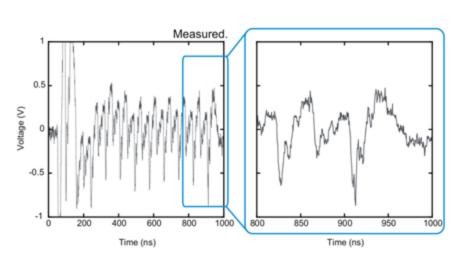

Fujimoto et al., EMC 2014

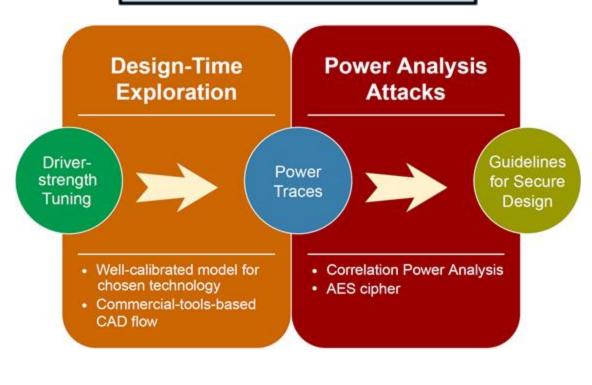

#### Motivation

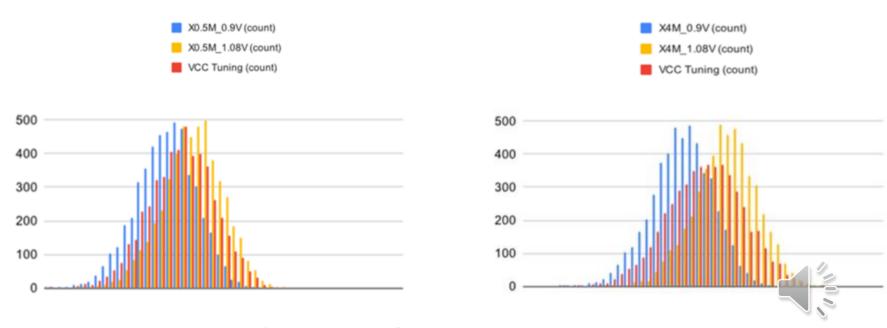

- VCC Tuning Countermeasure

- Improved impact when driver strength tuning is added.

Hardware Security Basics Motivation **Methodology** Setup Results Conclusion

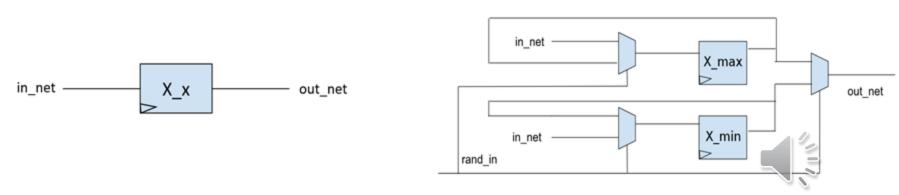

#### Runtime Tuning Implementation

- ASIC

- Static tuning: Reconfigure driver strength in chosen registers

- Dynamic tuning: Chosen registers replaced by register pair and MUX pair

- VCC tuning: Assume IVR

- FPGA

- Driver strength tuning: Connected via IO pins rather than additional registers

- VCC tuning: Use onboard IVR

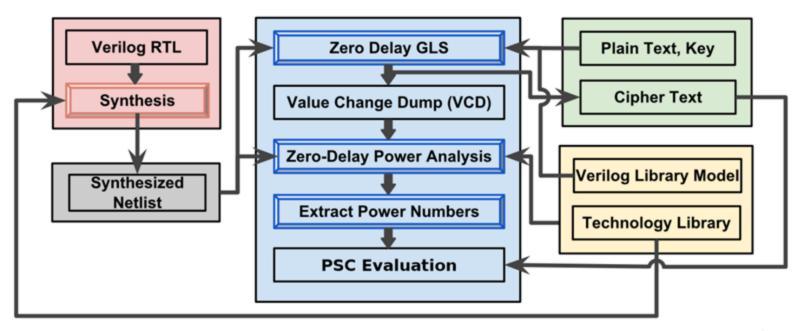

#### CAD Flow

### **CPA Setup**

## **PSC Evaluation**

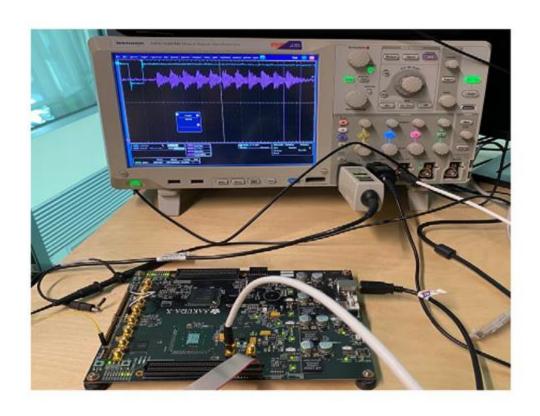

## FPGA Setup

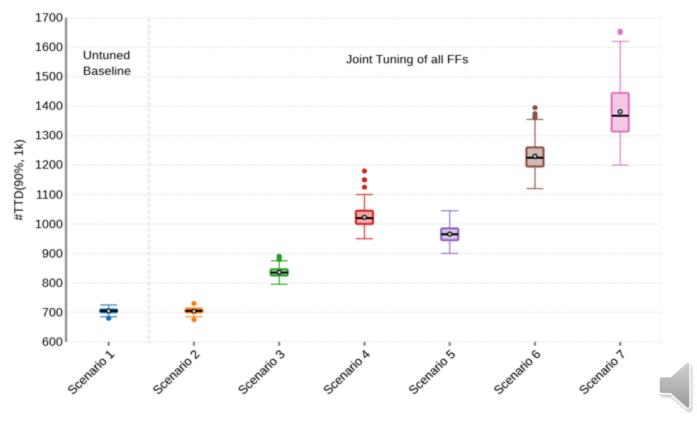

#### **ASIC CPA Results**

Results

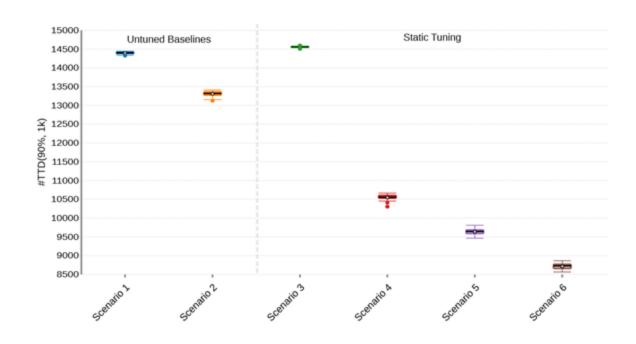

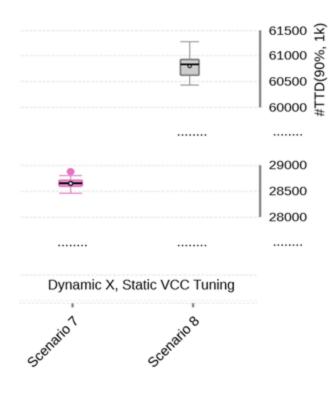

#### FPGA CPA Results

Motivation

Hardware Security Basics

## **ASIC Layout Analysis Results**

| Design      | Avg. Peak           | Critical-Path       | StdCell             |

|-------------|---------------------|---------------------|---------------------|

|             | Power [mW]          | Delay [ns]          | Area [μm²]          |

|             | 0.9V / 1.08V        | 0.9V / 1.08V        | 0.9V / 1.08V        |

| Baseline    | 2.709 / 3.100       | 9.64 / 9.79         | 54,928 / 43,639     |

| All FFs     | 3.134 / 3.764       | 14.13 / 11.86       | 67,873 / 57,300     |

| Tunable     | (+15.69% / +21.42%) | (+46.68% / +21.14%) | (+23.57% / +31.30%) |

| AES-Text    | 2.779 / 3.237       | 14.13 / 11.68       | 57,272 / 46,324     |

| FFs Tunable | (+02.58% / +04.42%) | (+46.68% / +19.31%) | (+04.27% / +06.15%) |

ASIC Layout Analysis

## FPGA Layout Analysis Results

Hardware Security Basics

| Design     | Avg. Peak<br>Power [mW]<br>0.9V / 1.08V | Critical-Path<br>Delay [ns] | FFs / LUTs<br>Util. [# / #] |

|------------|-----------------------------------------|-----------------------------|-----------------------------|

| Baseline   | 0.969357 / 1.07049                      | 9.052                       | 952 / 3,137                 |

| Static X4  | 0.972771 / 1.07352                      | 10.352                      | 965 / 3,118                 |

|            | (+00.35% / +00.28%)                     | (+14.36%)                   | (+01.37% / -00.61%)         |

| Static X16 | 0.971117 / 1.07347                      | 10.352                      | 965 / 3,118                 |

|            | (+00.18% / +00.27%)                     | (+14.36%)                   | (+01.37% / -00.61%)         |

| Dynamic    | 0.973676 / 1.07214                      | 9.994                       | 1,028 / 3,183               |

|            | (+00.45% / +00.15%)                     | (+10.41%)                   | (+07.98% / +01.47%)         |

**FPGA Layout Analysis**

#### Design Guidelines

Static tuning should be avoided.

Hardware Security Basics

- Dynamic tuning of both driver strength and VCC should be used when possible as it is most resilient.

- Dynamic driver-strength tuning is a preferred alternative compared to dynamic VCC tuning.

- Tuning all flip-flops is not always practical.

#### Conclusion & Future Work

- More efficient tuning implementation for ASIC and FPGA.

- Study tuning in the context of leakage power attacks.

- Further study using other approaches for security assessment.