VLSIR - A Modular Framework for Programming Analog & Custom Circuits & Layouts

Berkeley UNIVERSITY OF CALIFORNIA

Dan Fritchman ISPD 2023

### About Me

- Duke 2006

- Apple 2009-19

- Embedded systems

- SoC analog & mixed-signal IP

- Software therefore

- Berkeley 2020-present

- Software for AMS circuits

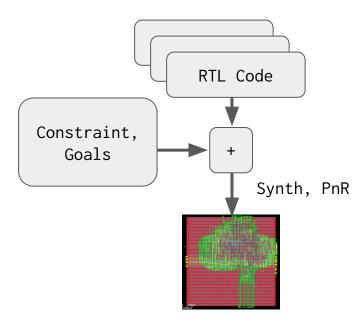

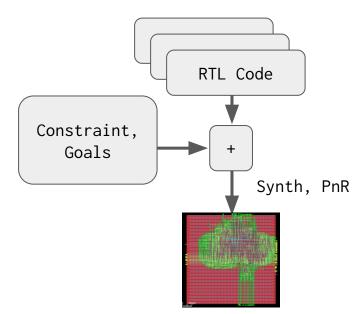

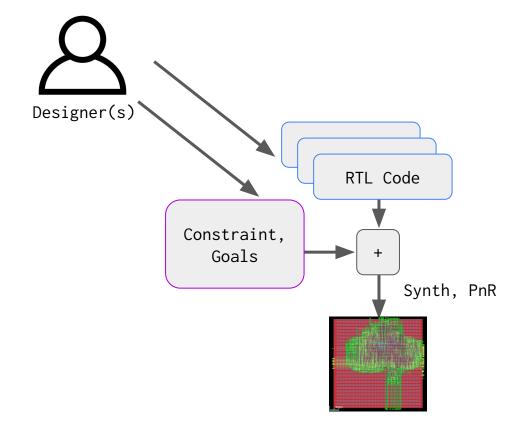

## The Two Ways 99.999% of IC Layout is Made

by compilation & constraints AKA digital PnR

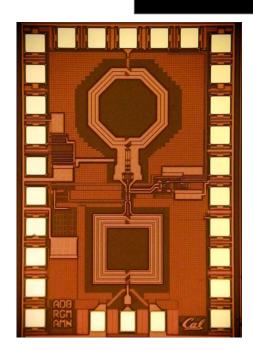

Full Custom

AKA by GUI Clicks

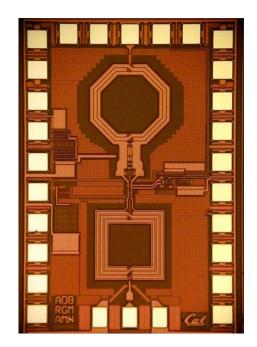

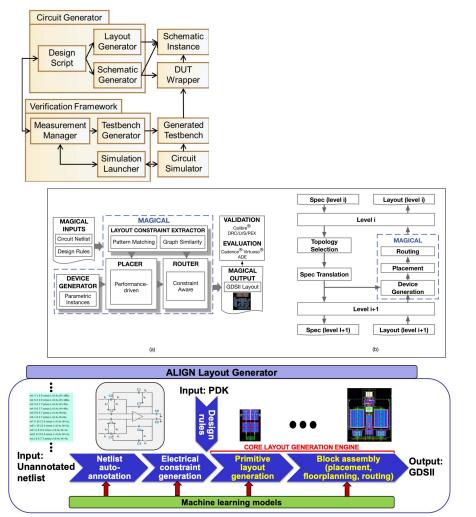

### Recent Prior Art

- ALIGN == analog layout intelligently generated from netlists

- MAGICAL == machine generated analog IC layout"

- BAG == Berkeley Analog Generator

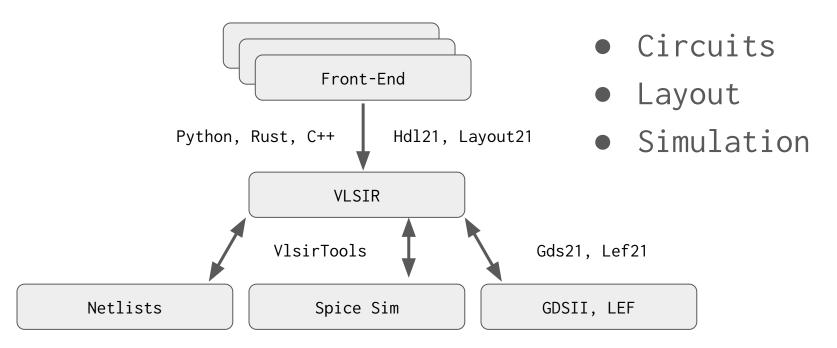

### VLSIR == Protobuf Design Database

### **Dinner Party Tests**

- Explain this to someone smart

- But not in the field

### Dinner Party Test #1:

```

print("Hello World!")

print("Hello Again")

if something:

print("Something is true")

a number = 5

while a number > 3:

print(a number)

a number = get a random number()

```

### Dinner Party Test #2:

```

Dinner Party

Test #3:

```

(MUCH) Harder

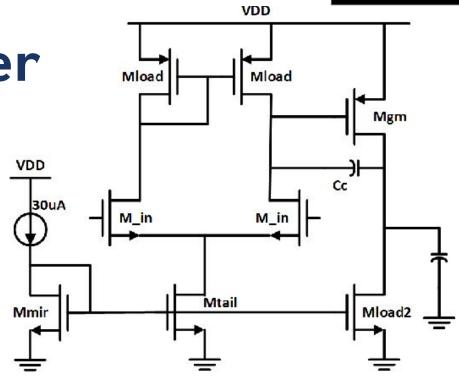

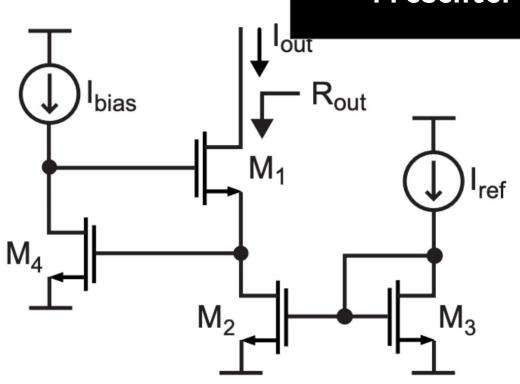

## Most Presenter Real (Bad) Schematics

Zoom

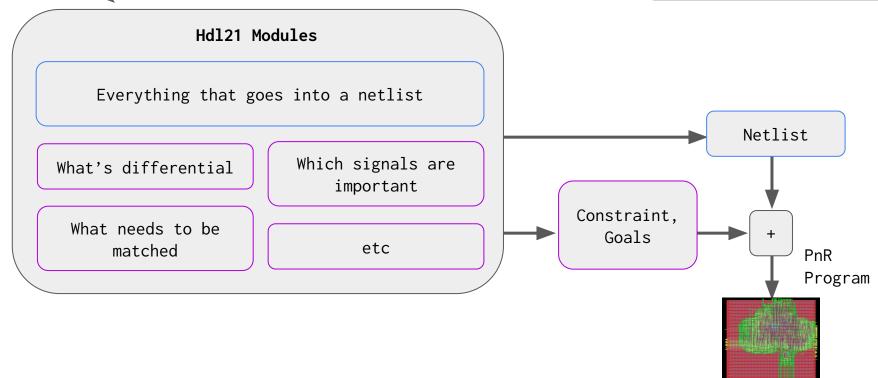

# Hdl21 == Analog HDL + Python

- For circuit designers

- Expose the concepts they know, in the most approachable language available (Python)

- Max productivity,

min fancy-programming

skill

```

import hdl21 as h

```

@h.module

class MyModule:

i = h.Input()

o = h.Output(width=8)

s = h.Signal()

a = AnotherModule(a=i, b=s, c=o)

```

@h.module

class Inner:

inp = h.Input()

out = h.Output()

```

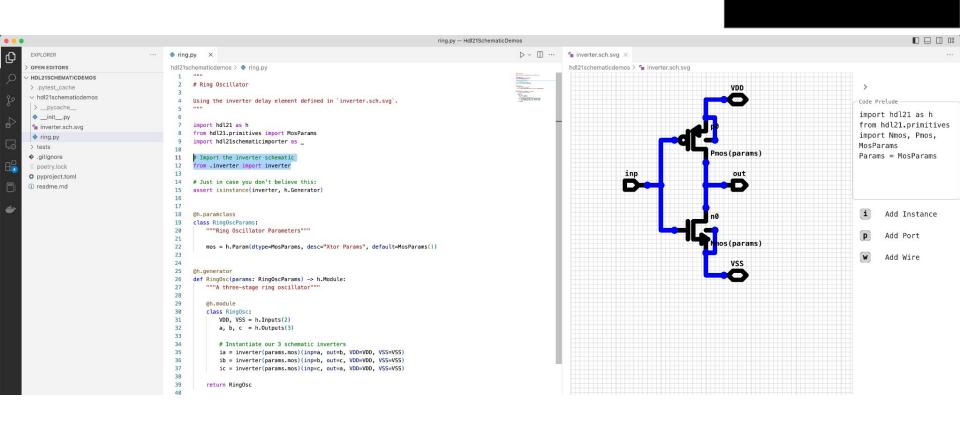

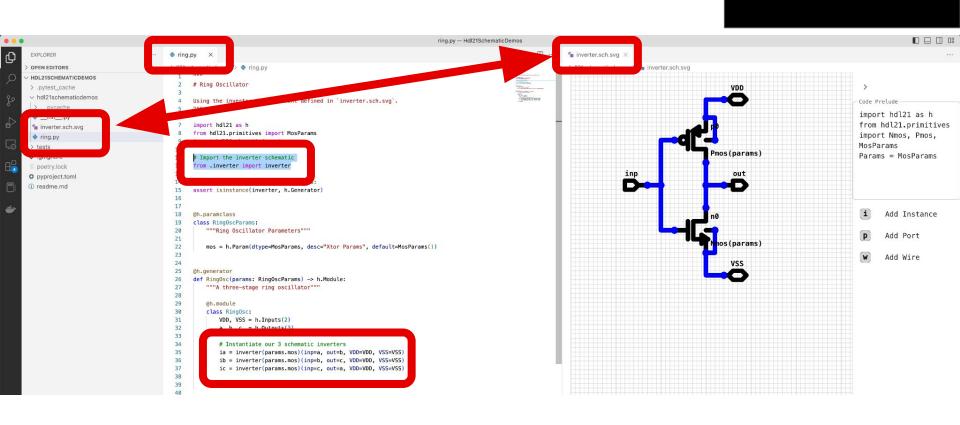

# Hdl21 Generator == f(Params) -> Module

# The Stuff Only an Analog-er Could Love

#### Zoom Presenter

- PDKs

- Generic primitives

- Compiling generics into PDKs

- PVT Corners

- Spice sims

- Diff pairs

- Matched arrays

- etc

```

@h.module

class Rlc:

@h.module

p, n = h.Ports(2)

class Tb:

res = h.Res(r=1*K)(p=p, n=n)

# All it takes to be a testbench

cap = h.Cap(c=1*\mu)(p=p, n=n)

VSS = h.Port()

ind = h.Ind(l=1*n)(p=p, n=n)

# Write a spice-format netlist to stdout

@h.sim # Using `mypdk.install`

h.netlist(Rlc, sys.stdout, fmt="spice")

class SimMyPdk:

tb = MyTestBench

@h.module

class Inv:

models = Include(

i, o, VDD, VSS = h.Ports(4) # Create some IO

path=mypdk.install.models

# And now create some generic transistors!

ps = Pmos(w=1*\mu, l=1*\mu, vth=MosVth.STD)(d=0, q=i, s=VDD, b=VDD)

ns = Nmos(w=1*\mu, l=1*\mu, vth=MosVth.STD)(d=0, g=i, s=VSS, b=VSS)

SimMyPdk.run()

# Run it!

import sky130

```

sky130.compile(Inv)

# Bundle == struct conn Diff == a special Bundle Pair == two identical Instances

```

@h.bundle

class Diff:

p, n = h.Signals(2)

@h.bundle

class QuadratureClock:

i = Diff() # In-phase component

q = Diff() # Quadrature component

```

```

@h.module

class DiffAmp:

i = h.Diff()

o = h.Diff()

bias, VDD, VSS = h.Inputs(3)

ni = Nbias(g=bias, s=VSS)

ns = h.Pair(Ninp)(s=ni.d, g=i, d=o)

rl = h.Pair(Rl)(p=o, n=VDD)

```

## My General Outlook:

# MOST Schematics are BAD

My General Outlook:

## MOST Schematics should be code

### **But There Are**

Some

Awesome

Schematics

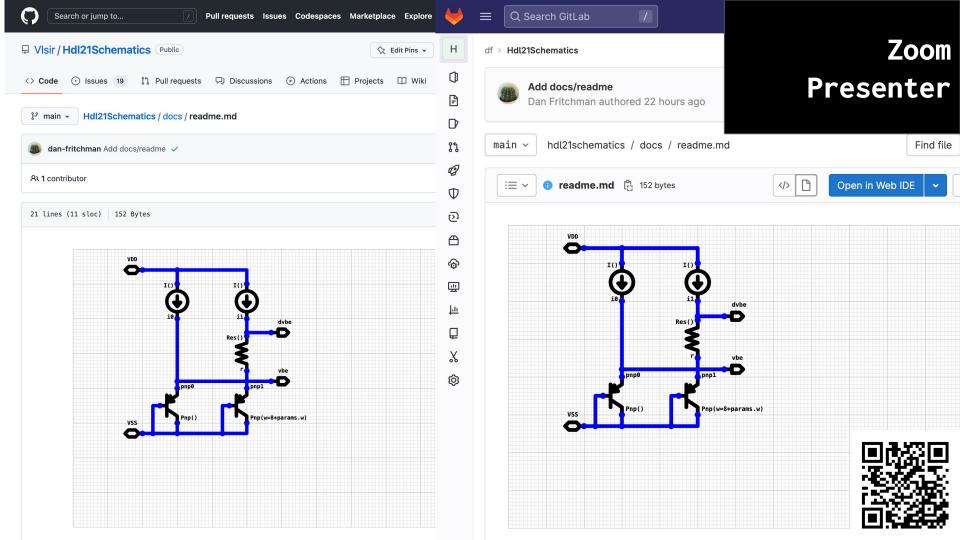

- Schematics are **SVG images**

- Single file, no dependencies, no "database"

- Every modern browser & OS can render

- Schematics are "graphical Python modules"

- Import as hdl21 Generators

## Zoom Presenter

#### Zoom Presenter

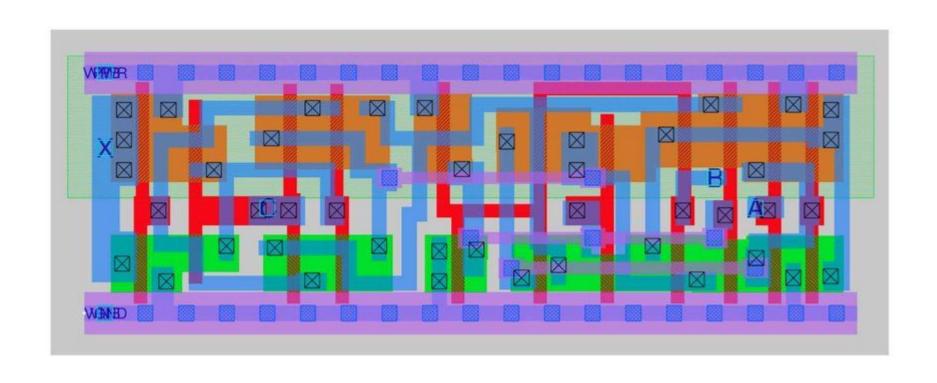

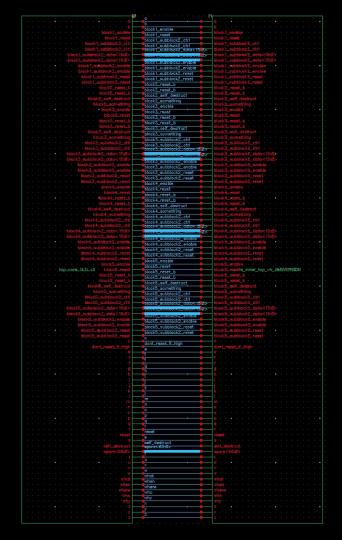

# The Two Ways 99.999% of IC Layout is Made

by compilation & constraints AKA digital PnR

Full Custom

AKA by GUI Clicks

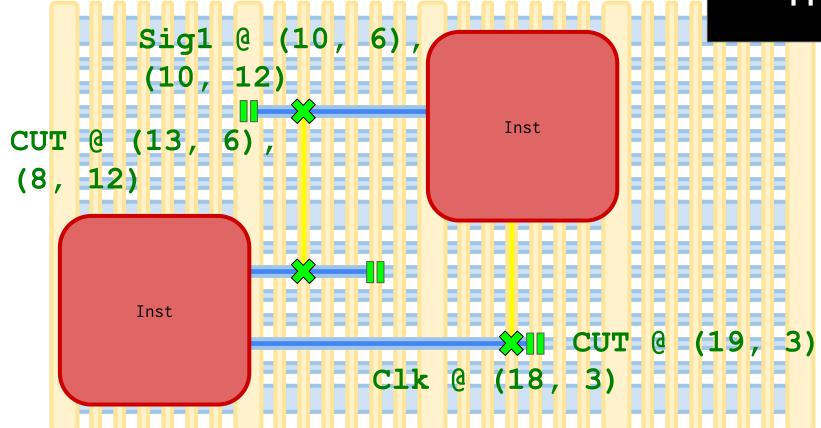

### Tetris Routing

Zoom Presenter

### Zoom Presenter