# ON THE WAY TO PRACTICAL TOOLS FOR BEYOND DIE CODESIGN AND INTEGRATION

Honoring Prof. Yoji Kajitani 梶谷洋司先生 ISPD 2013

#### Experience I hope the audience to have

- Honoring Prof. Kajitani

- By showing some traces of exploration path

- Enjoying this talk

- Embedded 5 research problems (actually 6)

#### Outline

- Prof. Kajitani I know

- The beginning

- Problem 0

- Inspirations from Prof. Kajitani

- Problem 1

- Influences

- Problem 2-4

- Collaboration, visit and exploration

- Taiwan company visits and forums

- Problem 5

- Stepping into the future of beyond die tools

### Kajitani: The "Coding" Master

- Famous sequence pair representation for floorplanning/placement

- Influenced countless researches

- Also an artist

- Very easy-going and amiable

- Likes to swim and walk very much

- Hard-working

- Many more...

# The Beginning

- 2008, lucky year to me

- Got an invitation to work together

- Why do I have this honor?

- 2007 ASPDAC paper

- I am Martin's student ©

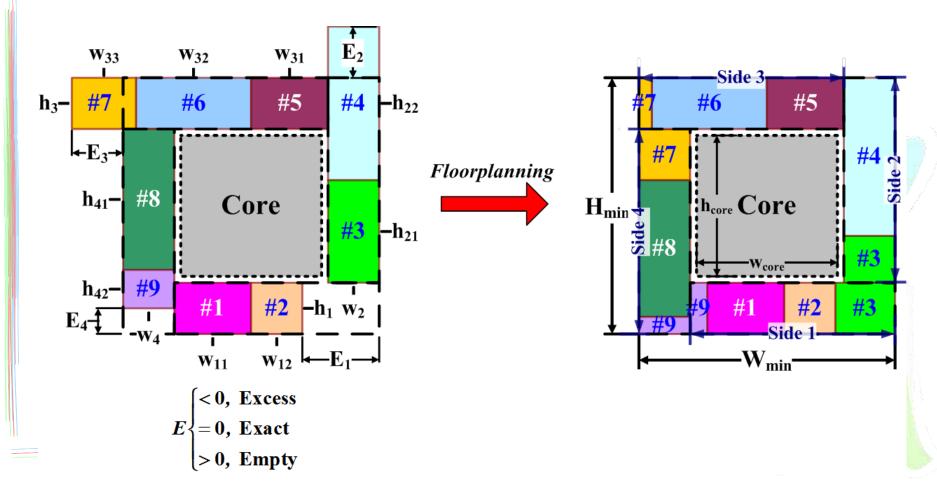

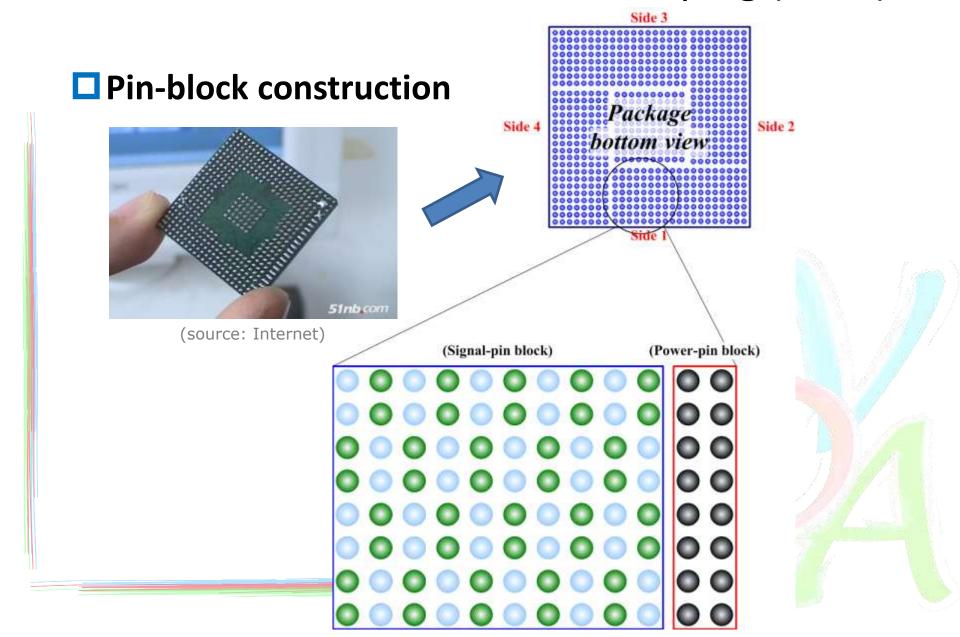

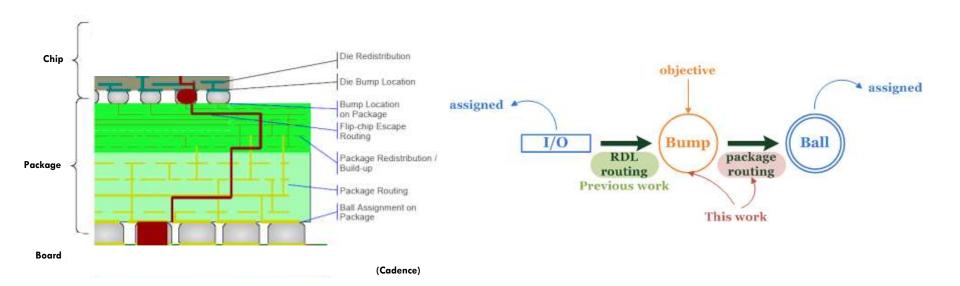

# Problem 0: Fast Flip-Chip Pin-Out Designation by Pin-Block Design and Floorplanning

R.-J. Lee and H.-M. Chen

ASPDAC 2007 and TVLSI Aug 2009

#### **Constraints and Considerations**

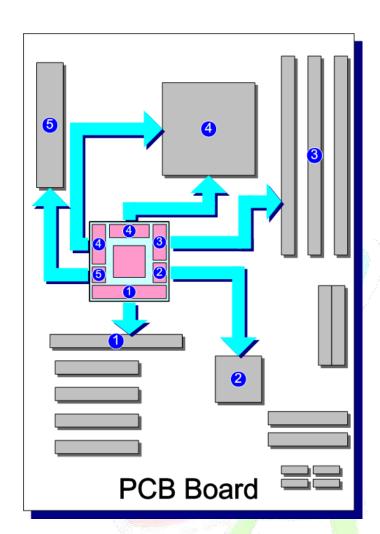

#### □ Locations of PCB components

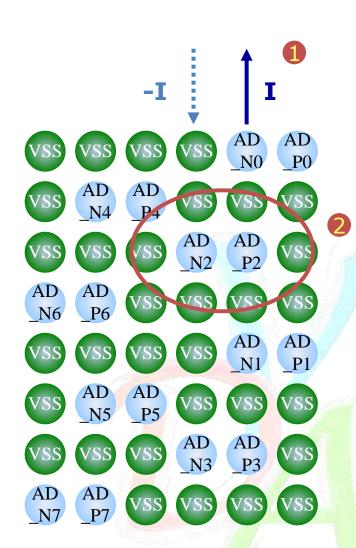

Reducing SSN noise

$$V_{SSN} = NL_{tot} \frac{dI}{dt}$$

$V_{SSN}$ : Simultaneous Switching Noise

*N*: Number of drivers switching

$L_{tot}$ : Equivalent inductance in current loop

Facilitating PCB planar routing

### Constraints and Considerations (cont.)

### Constraints and Considerations (cont.)

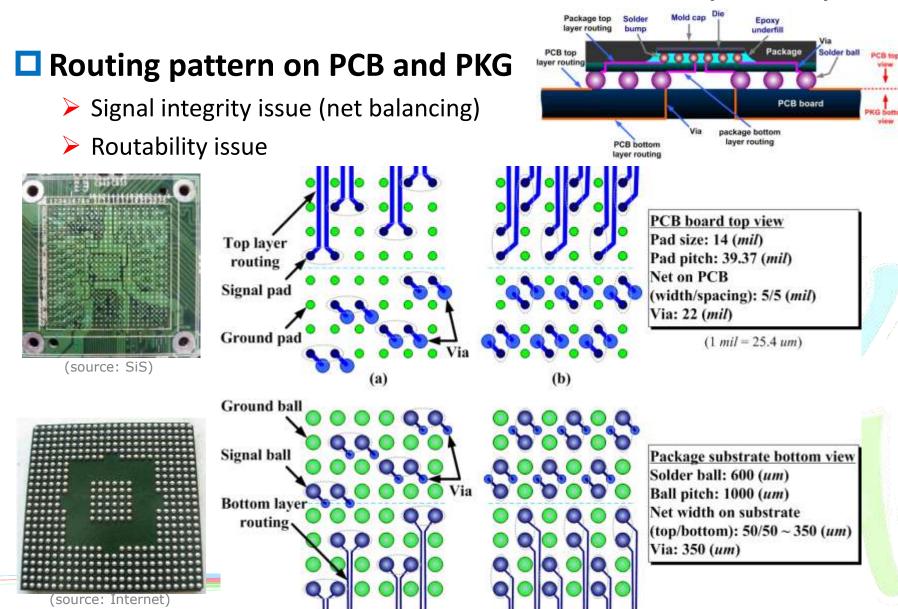

#### ■Signal integrity issue

- Return path pin

- Shielding pin

$$I_{noise,C_m} = C_m \frac{dV_{driver}}{dt}$$

$I_{noise,C_m}$ : Noise induced by mutual capacitor

$C_m$ : Mutual capactance

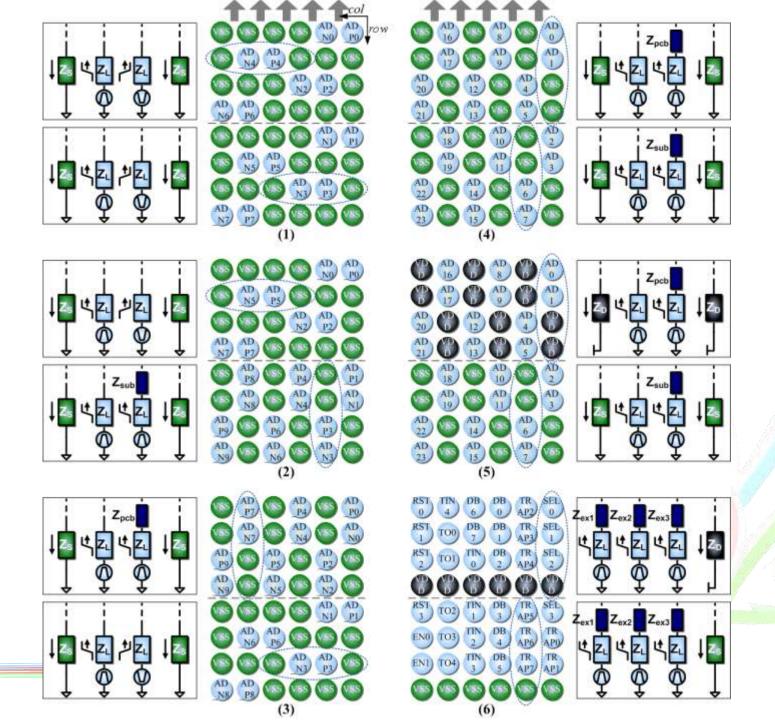

## Pin Pattern Design

#### □ Characteristics of signal-pin patterns

|              | Application                                  | Signal-<br>pin NO. | Pin-to-pin<br>crosstalk<br>immunity | Net balance |              |                   |              | Signal shielding on<br>package substrate |              | Power    | Pin-        |

|--------------|----------------------------------------------|--------------------|-------------------------------------|-------------|--------------|-------------------|--------------|------------------------------------------|--------------|----------|-------------|

|              |                                              |                    |                                     | PCB board   |              | Package substrate |              | (VDD/VSS)                                |              | delivary | designation |

|              |                                              |                    |                                     | Top layer   | Bottom layer | Top layer         | Bottom layer | Top layer                                | Bottom layer | aware    | efficiency  |

| Pattern<br>1 | Differential signal                          | 16                 | Excellent                           | Good        | Good         | Good              | Good         | vss                                      | vss          | Without  | Not good    |

| Pattern<br>2 | Differencial signal /<br>Single-ended signal | 20                 | Good                                | Good        | Good         | Good              | Not good     | VSS                                      | vss          | Without  | Average     |

| Pattern<br>3 | Differencial signal /<br>Single-ended signal | 20                 | Good                                | Not good    | Good         | Good              | Good         | vss                                      | vss          | Without  | Average     |

| Pattern<br>4 | Differencial signal /<br>Single-ended signal | 24                 | Excellent                           | Not good    | Good         | Good              | Not good     | VSS                                      | vss          | Without  | Good        |

| Pattern<br>5 | Differencial signal /<br>Single-ended signal | 24                 | Excellent                           | Not good    | Good         | Good              | Not good     | VDD                                      | vss          | With     | Good        |

| Pattern<br>6 | Single-ended signal                          | 36                 | Not good                            | Not good    | Not good     | Not good          | Not good     | None                                     | None         | With     | Excellent   |

#### Pin-Block (PB) Construction and Grouping

□ PB construction → PB grouping → Rough PB plan

→ Min. PKG size → PB floorplanning → Final PB plan

#### Pin-Block Construction and Grouping (cont.)

# **Start to Work Together**

### Inspiration/Work from Collaboration

- Introducing Problem 1

- Came from a training assignment for students

The legacy of sequences

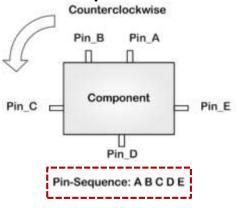

# Problem 1: Escaped Boundary Pins Routing for High Speed Boards

C.-Y. Chin, C.-Y. Kuan, T.-Y. Tsai, H.-M. Chen, and Y. Kajitani

DATE 2010 and TCAD March 2013

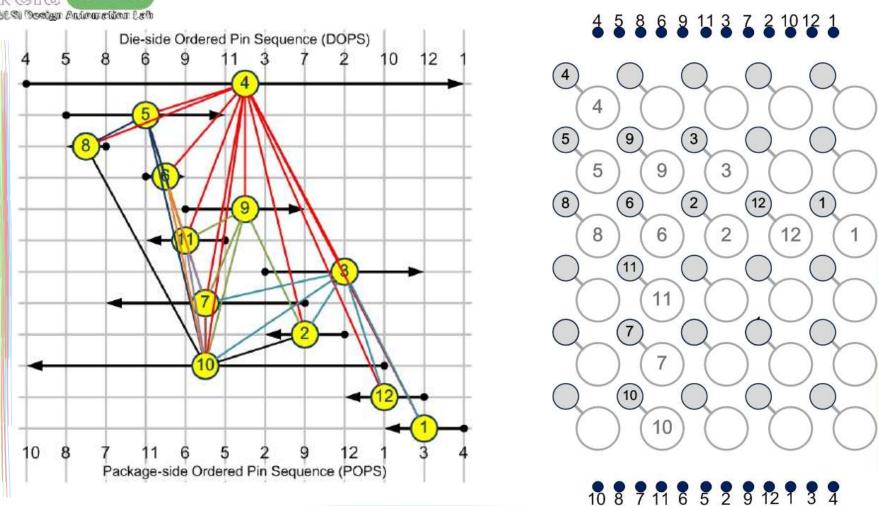

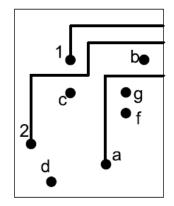

# Routing under Fixed-Ordering Pin Locations

#### Pin sequence

Connected Component Point (CCP)& Dynamic Pin Sequence (DPS)

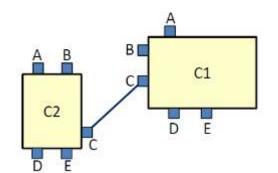

CCP: C

Pin-Seq C\_1: ABCDE

Pin-Seq C\_2: BADEC

**DPS: ABBADECCDE**

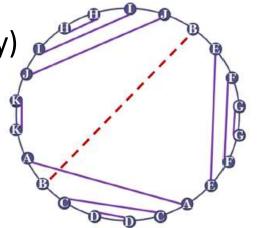

#### Multiple components

component pins

boundary pins

CCPs: C, G, I

DPS:

KHHKJ<u>II</u>JBEF<u>GG</u>FDDEA<u>CC</u>BA

# Routing under Fixed-Ordering Pin Locations

#### CCP Selection

Generation of maximum weight spanning tree. The component with the largest connectivity is chosen to be the base DPS (C\_1 here).

# Routing under Fixed-Ordering Pin Locations

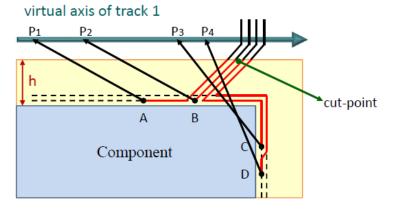

Against-the-wall routing (similar to Boundary Routing)

Either net B or net A is unroutable

- Routing order determination(max routability)

- Supowit's algorithm

r q q corresponding circle graph

DPS: HIJBEFGGFEACDDCBAKKJIH

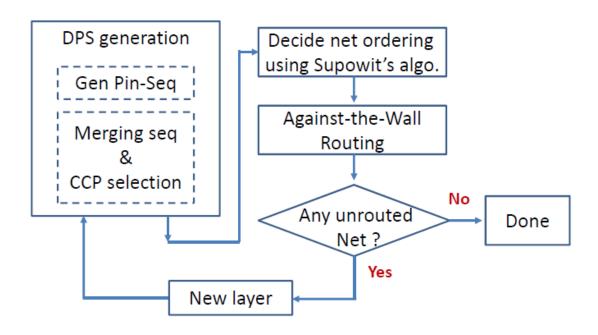

# First Stage Routing: Topological

Overall flow of the topological routing

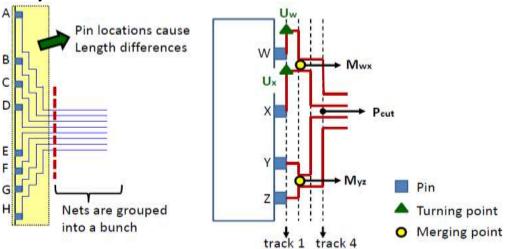

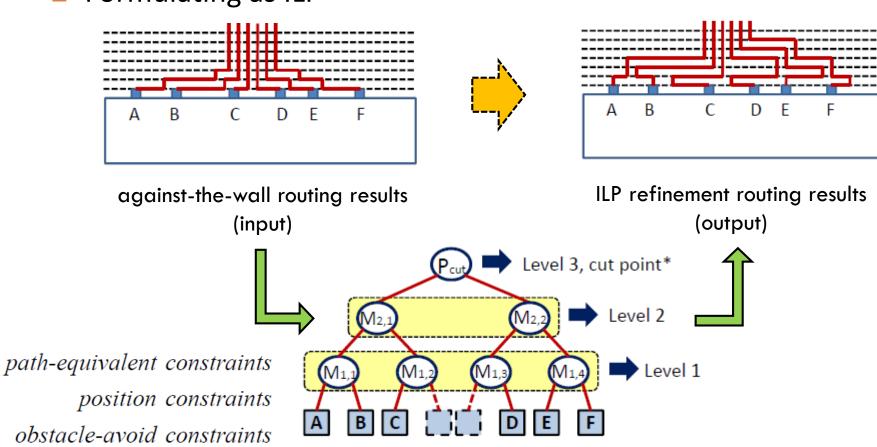

### Second Stage Routing: Length-Constraint-Aware Routing Refinement

Key idea

Mapping pin locations to 1-D coordinates

# Length-Constraint-Aware Routing Refinement

#### Formulating as ILP

Merging tree of the ILP formulation

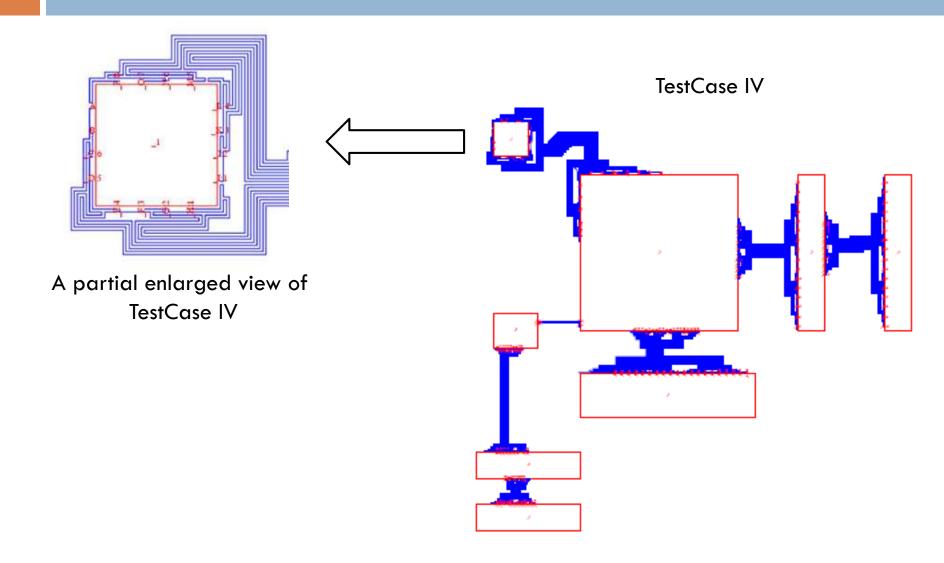

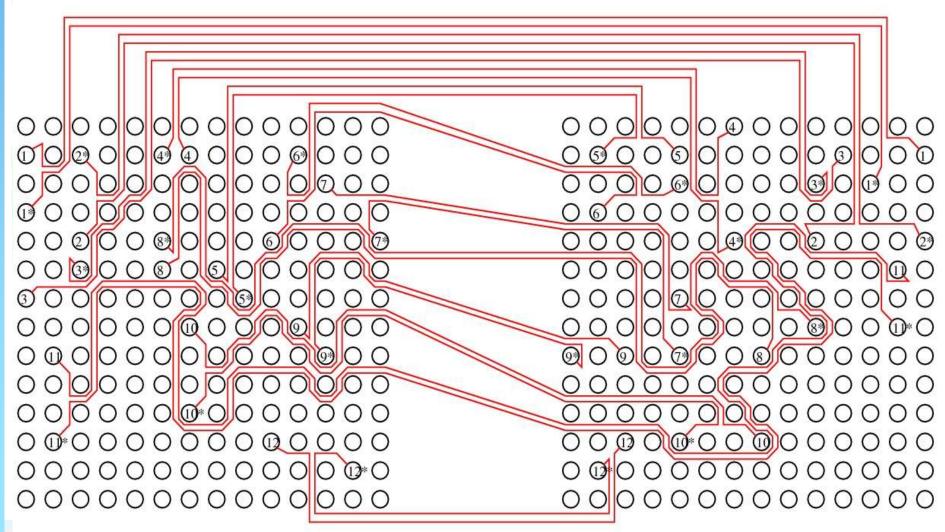

# Routing Instance

#### Influences in Research

After years of collaboration and discussion, we also come up with our own works influenced by it

- Introducing Problems 2-4

- Some are related to Martin's works

# Problem 2: Board- and Chip-Aware Package Wire Planning

R.-J. Lee, H.-W. Hsu, and H.-M. Chen

IEEE TVLSI Sep 2012

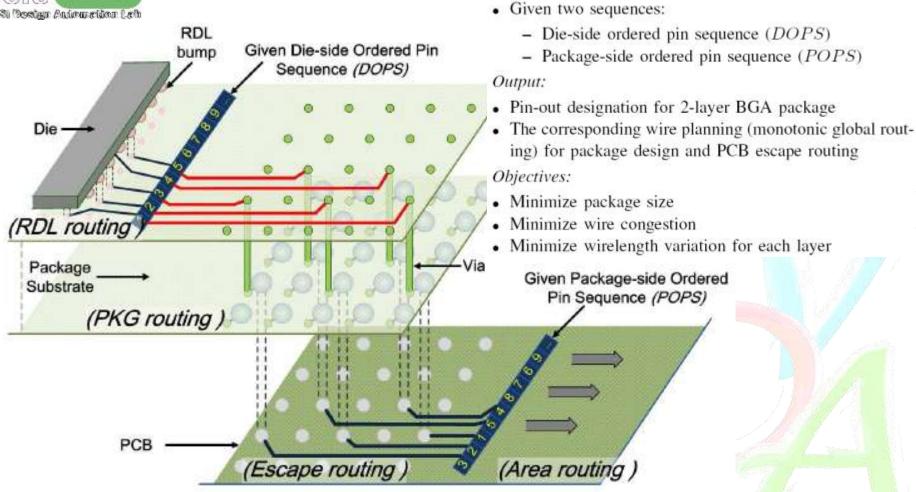

#### Our Problem

Input:

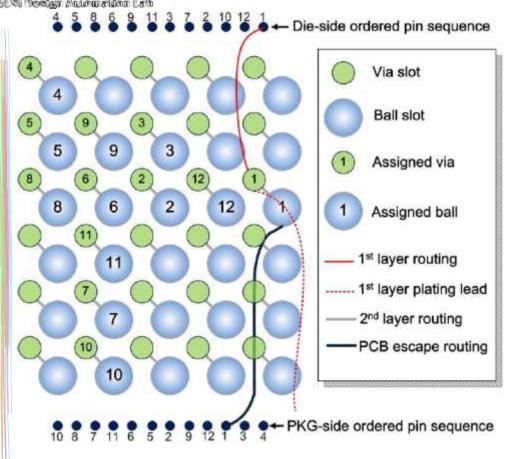

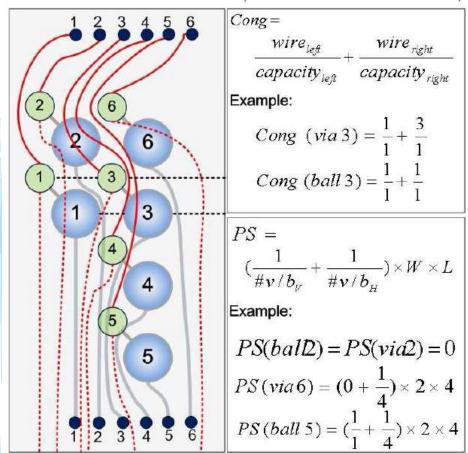

# 2-Layer BGA Model

- BGA model

- Via in a grid pattern

- Empty un-used slot

- Assigned via/ball

- 2-layer package

- Top layer: DOPS to via

- Bottom layer: via to ball

- Printed circuit board

- Ball to POPS

#### Observations

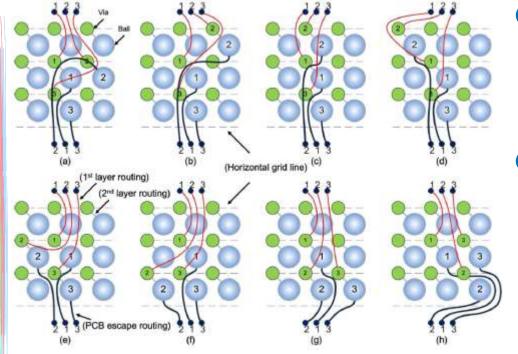

- Monotonic routing

- Along one direction

- No turn back

- For net1/net2

- 1. (a)(e) not monotonic

- (b)(d)(f)(h) monotonic but use more columns

- 3. (c) (g) monotonic

Rule1: assign to different row if orderings are reverse Rule2: assign to same column to reduce package size

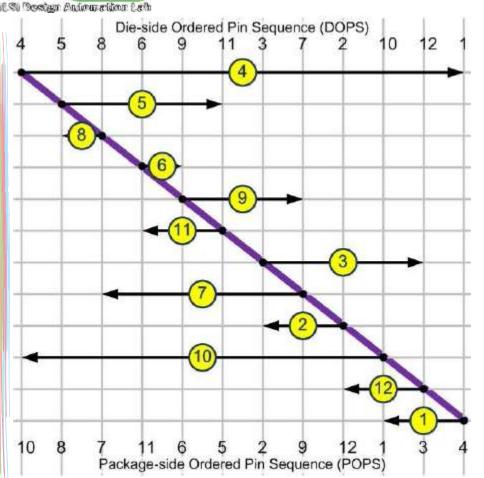

### Interval Diagram

- Analyze DOPS and POPS

- Build an edge if ordering is reverse

## Initial Pin-Out Designation

# Cost Evaluation: Congestion, Length Difference, Package Size

$$Cost_{vi/bi} = \alpha \times Cong_{vi/bi} + \beta \times Diff_{vi/bi} + \gamma \times PS_{vi/bi}$$

$$Diff_{vi/bi} = dist(v_i/b_i) - dist(avg)$$

- Cost of via/ball

- Calculated separately

- Summed up in opt.

$$cVGA = \sum_{i=0}^{n} Cost_{vi}$$

$$cBGA = \sum_{i=0}^{n} Cost_{bi}$$

$$Sum = cVGA + cBGA$$

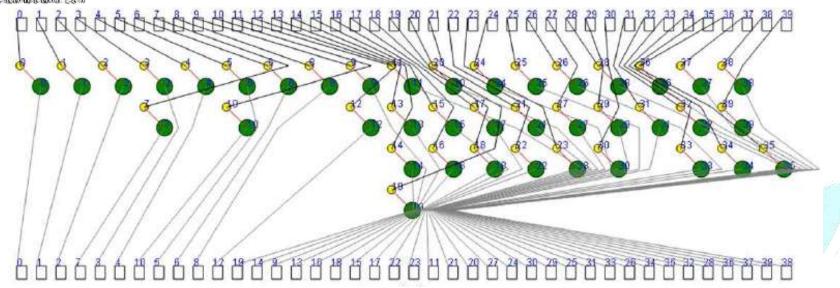

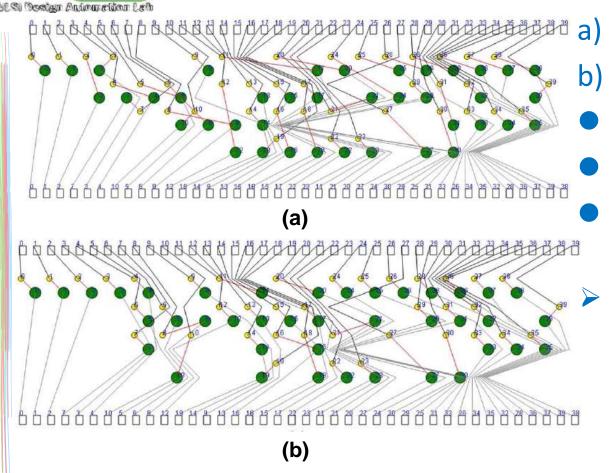

# Wire Planning Instance

Initial solution

### Wire Planning Instance

Greedy-full mode

LPC-full mode

Lower congestion

Lower length variation

Almost the same package size

Trade-off between routability and package size

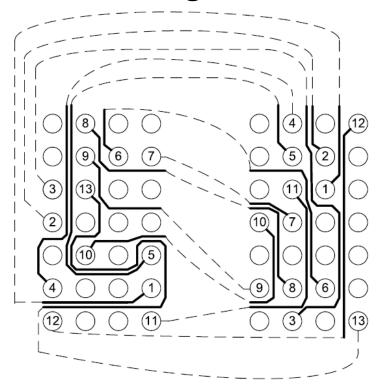

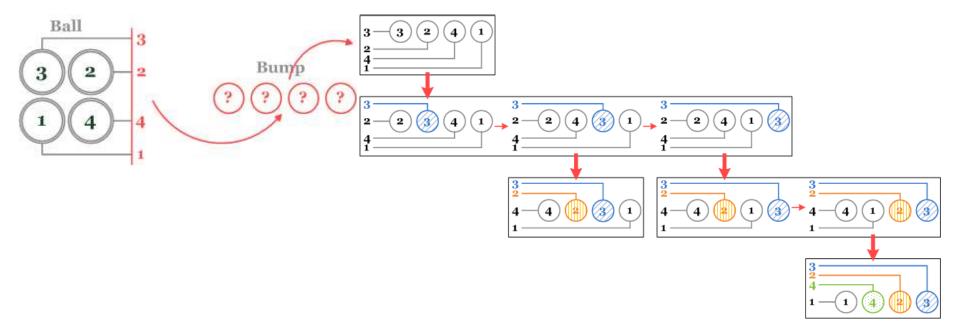

# Problem 3: BGA Bump Assignment for Chip-Package Codesign

M.-L. Chen and H.-M. Chen

#### **Problem Formulation**

#### Given

- I/Os assignment

- Balls assignment

#### Objective

- Find a solution of bump assignment

- × number of tracks on RDL routing is minimized

- × routability of package route is maximized

# Simultaneous Escape Routing

To find planar escape solutions in both components so that they are honoring the same escape ordering.

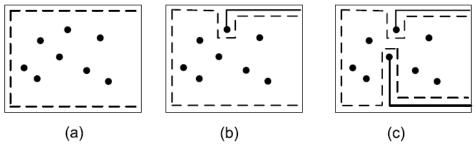

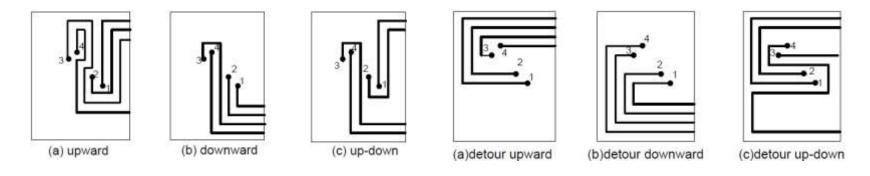

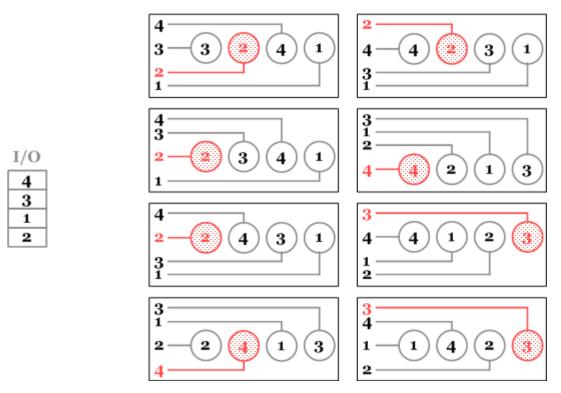

# **Boundary Routing**

Define routing boundary as the boundary of the maximum routable region of the unrouted pins.

6 routing modes

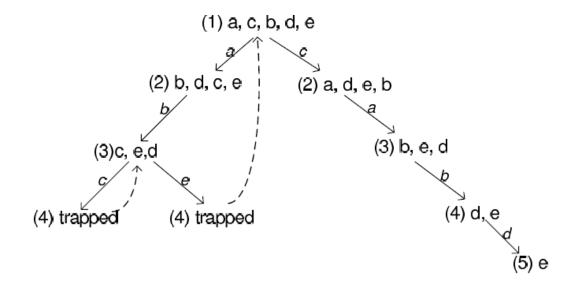

## **Dynamic Net Ordering**

- $\square$  Define routing cost vector ( $\alpha$ ,  $\beta$ )

- $\square$  # of pins **trapped** (unroutable) by routing current,  $\alpha$

- # of pins blocked (but still routable) by current routing, β

Cost of Net a:  $(\alpha, \beta)$

Trap b :  $\alpha = 1$ Block c :  $\beta = 1$

### **B-Escape Routing Algorithm**

```

1: for each of the six routing modes do

2:

repeat

for each unrouted net i do

route Net i in the left component by current mode

route Net i in the right component by current mode

5:

calulate the cost vector for Net i

6:

clear the routes generated for Net i

7:

end for

8:

9:

choose the net j with minimum cost

if Net j traps other nets then

10:

backtrack and reorder

11:

12:

else

route Net j in the left component by current mode

13:

route Net j in the right component by current mode

14:

end if

15:

until all nets are routed or exceed the backtrack limit

16:

store the solution for this routing mode

17:

18: end for

19: output the solution with the best routability

```

# What We Proposed: Using B-Escape for Package Routing

```

1: for each of the six routing modes do

2:

repeat

for each unrouted net i do

3:

route Net i in package by current mode

5:

calulate the cost vector for Net i

6:

clear the routes generated for Net i

7:

end for

8:

choose the net j with minimum cost

9:

if Net j traps other nets then

10:

backtrack and reorder

11:

12:

else

13:

route Net i in package by current mode

14:

end if

15:

until all nets are routed or exceed the backtrack limit

16:

store the solution for this routing mode

17:

18: end for

19: output the solution with the best routability

```

# Bump Assignment (1/2)

Find bump assignment according to the package escape routing result.

# Bump Assignment (2/2)

Choosing a solution from bump assignment to minimize the difference between bump pin order and I/O pin order

# Problem 4: Simultaneous Escape Routing for Diff Pairs and Multiple Components

C.-Y. Chin, Y.-J. Lee, and H.-M. Chen

#### **B-Escape: Not Aware of Diff Pairs**

#### Diff Pairs Aware B-Escape

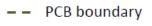

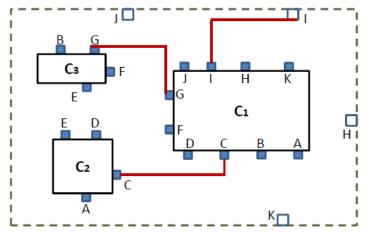

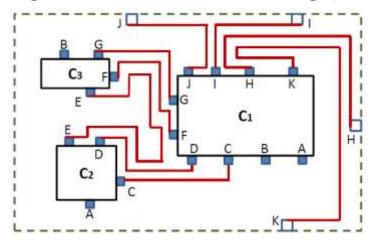

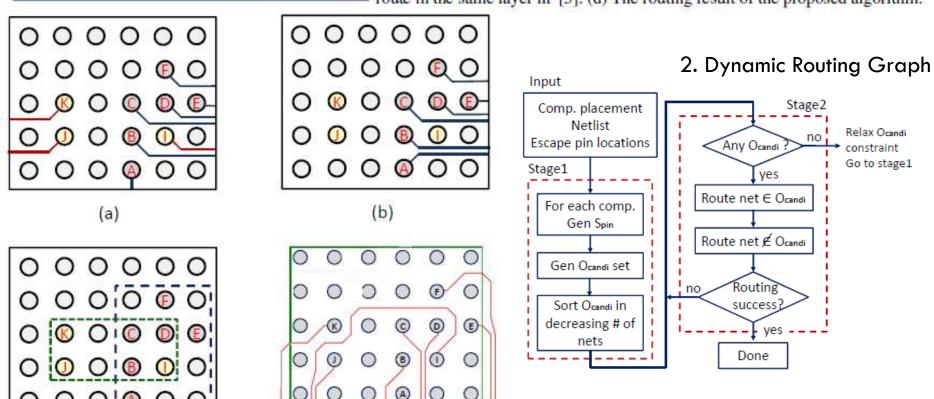

# Simultaneous Escape in Routing Multiple Components

Fig. 1.

component need to be escaped. (a) The routing result is illegal: net I belongs to  $B_2$  but not  $B_1$ , (b) The routing result of  $B_1$ , net I is blocked, (c) The rectangle representation of the two busses, they are overlapped and cannot Bus B\_1 =  $\{A,B,C,D,E,F\}$  Bus B\_2 =  $\{I,J,K\}$ route in the same layer in [5]. (d) The routing result of the proposed algorithm.

(d)

(c)

#### Stage2 Relax Ocandi Any Ocandi constraint Go to stage1 yes Route net ∈ Ocandi

Route net ∉ Ocandi

Routing

success?

Done

1. Topological routing

An illustration of routing problem when multiple busses of a

# of nets: 34 # of busses: 4 (3) 3 3 1 2 (G) 0 W (3) (B) 1 0 (1) 9 0 8 0 (B) 6 ® ® (3) @ (5) (E)

### Visits, Forum, and Exploration

- Other attempts

- Dr. Murata's visit in 2008

- 2009 Japan-Taiwan EDA Science and Technology Symposium

- EDA forum 2010@Taiwan

- Visits to AsRock, Faraday, GUC

- Introducing Problem 5

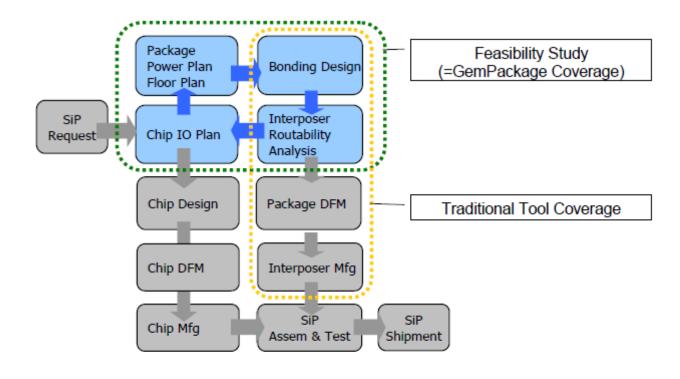

### GemPackage by Dr. Murata

#### Concept: Just For Feasibility Study

#### Taiwan EDA Forum 2010

Length Aware Routing and Clock Tree Design

Yoji Kajitani (梶谷洋司) The university of Kitakyushu, Japan

臺灣國科客座教授(Nov. 2010-Jan. 2011)

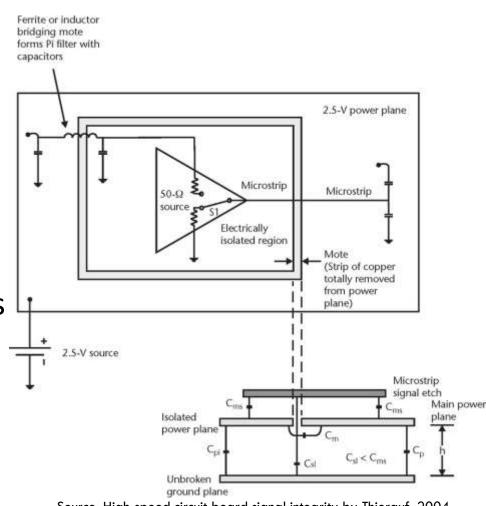

# Problem 5: PCB Routing Considering Motes

#### What is Mote?

- During our several visits to board design companies, we heard about power islands

- It is called *Motes*

- Split-plane situation

- A total break in the copper plane, forming an isolated region

- This technique is often used to form unique power islands that connect either to a voltage different from the rest of the plane or to the same voltage through a PI filter

Source: High-speed circuit board signal integrity by Thierauf, 2004

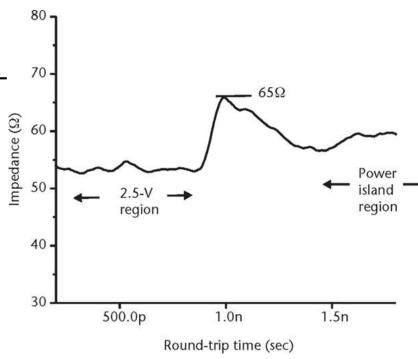

#### Problem when Signal Crossing a Mote

- An increase in inductance and reduction in capacitance causes the impedance to increase

- Therefore it is best to move motecrossing signals to a routing layer that has an unbroken return path

- Differential signaling is sometimes used to cross motes

TDR of a signal-crossing a mote

# Summary

#### **Conclusion 1**

- We are on the way.?(summary of attempts I know so far)

- Prof. Martin Wong and Prof. Kajitani in board routing

- Prof. YW Chang and me and others in chip-package/packageboard codesign

- Prof. XL Hong and others in package routing

- Practical automation tools for board design and codesign of board/system-package-chip are hard to come by (why?)

- Situations are very similar what we experienced in analog design automation tools

- We can discuss offline if more people are interested

- The future of this direction

- Based on the demands from the industry

#### **Conclusion 2**

- I am really honored and happy to work with Prof.

Kajitani in these years

- He is considered my another mentor in my research path: how to dedicate more in research

- I also get to know some of his students and become good friends

- I really hope the people down below have enjoyed my presentation

- Let us welcome Prof. Kajitani's intriguing talk!