# RC(L) Interconnect Sizing with Second Order Considerations via Posynomial Programming

Tao Lin and Lawrence T. Pileggi

Dept. Electrical and Computer Engineering

Carnegie Mellon University

#### **Outline**

- Elmore delay based formulation

- Central moment metrics

- Posynomiality of central moments

- Extension to inductive interconnects

- Applications

- Experiment results

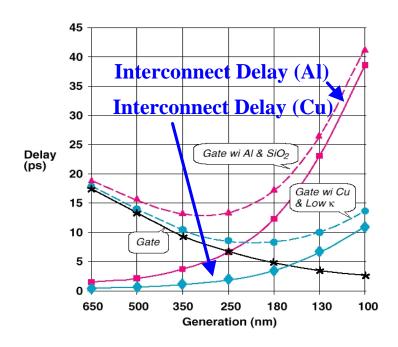

#### Interconnect Problem

- The delay due to the global RC(L) interconnects is becoming a dominant portion of the overall path delay

- Practical interconnect optimization methods are required for global nets

## **Optimization Via Elmore Delay**

Interconnect sizing formulations based on the Elmore delay model:

```

minimize Area(W) — Minimize the area subject to Elmore_k(W) \le d_0 — Delay constraints and \underline{w}_i \le w_i \le \overline{w}_i i = 1,...N — Width bounds

```

- Many efficient algorithms have been developed:

- Lagrange relaxation method

- Sensitivity based convex programming

- Local refinement algorithm

- Sequential quadratic programming

#### **Posynomiality of Elmore Delay**

- Elmore delay is the first order metric of RC interconnect delay

- □ The first moment:  $H(s) = m_0 + m_1 s + m_2 s^2 + ...$

- □ Sum of RC products: Elmore  $_k = \sum_{i \in P(k)} R_i \sum_{j \in D(i)} C_j$

- Function of width:  $R_i \propto \frac{1}{w_i}$   $C_i \propto w_i$   $Elmore_{k}(w) = \sum_{i \in P(k)} (\frac{1}{w_i}) \sum_{j \in D(i)} a_{ij} w_j$

- Posynomial function of sizes:

- □ Posynomiality:  $f(w_1 \cdots w_n) = \sum a_i (\Pi w_j^{b_{ij}}), a_i > 0$

## **Posynomial Programming**

Posynomial geometric programming:

minimize

$$Area(W)$$

—  $Sum \ of \ w_i * l_i$

$subject \ to \ Elmore_k(W) < d_0$  —  $Delay \ constraints$

$and \ \underline{w}_i \le w_i \le \overline{w}_i \ i = 1,...N$  —  $Width \ bounds$

A posynomial function can be transformed into a convex function under the exponential substitution:

$$w_j = exp(x_j)$$

The interconnect sizing problem is a convex programming problem under exponential substitution

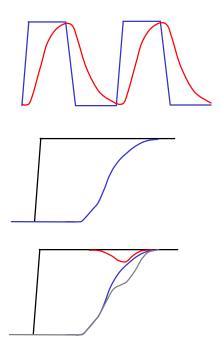

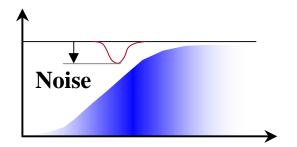

#### **Signal Integrity Problems**

- Signal integrity becomes an important issue in giga-scale DSM design

- Signal quality

- Clock attenuation

- Signal transition time

- Signal uncertainty

- Noise peak

- Extra-delay due to noise

#### **Higher Order Moments**

- Limitation of first order metrics

- Incapable of modeling integrity

- Incapable of modeling noise

- High order moments:

- It is trivial to show that higher order moments (RC trees) are also posynomial

$$m_{2,k} = \sum_{i \in P(k)} R_i \sum_{j \in D(i)} m_{1,j}$$

But reduced order models in terms of higher order moments do not preserve posynomiality

$$0.5 = 1 - a_1 e^{-p_1 t} - a_2 e^{-p_2 t} - \dots$$

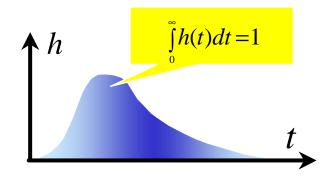

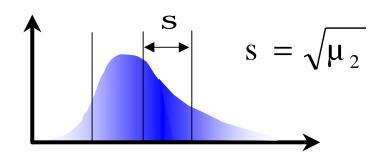

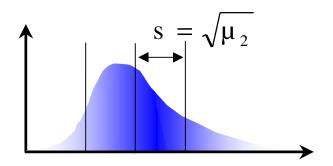

#### **Central Moments**

Definition of the central moments

$$\mathbf{m} = m_1 \equiv mean$$

$$\mathbf{m}_2 = 2m_2 - m_1^2$$

(variance)

$$\mathbf{m}_3 = -6m_3 + 6m_1m_2 - 2m_1^3$$

(skewness)

- - Standard deviation

- Dispersion

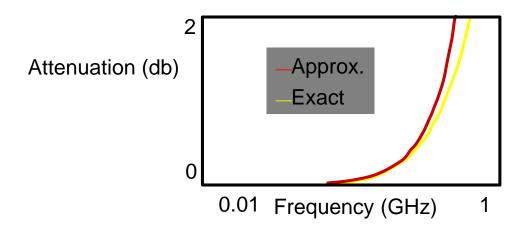

#### **Signal Attenuation**

An accurate model for signal attenuation in RCL clock tree [Celik99]

$$\mathbf{a}(\mathbf{w}) = -10\log(1 - \mathbf{m}_2\mathbf{w}^2) \quad (db)$$

A provable upper bound for RC responses

An upper bound for overdamped cases (RCL)

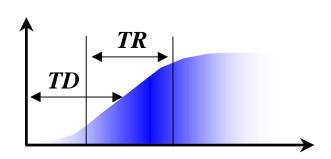

## **Signal Transition**

□ Transfer function:

$$g(s) = 1 - sTD + 0.5s^2(TR^2/2 + TD^2)$$

□ Signal transition time:  $TR = \sqrt{2p \, m}_2$

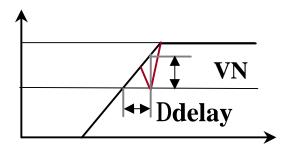

#### **Delay Due To Crosstalk**

- - Assuming a finite ramp input TR and an environment noise Vn

- Worst case alignment: ∆delay=TR\*Vn/Vdd

## **Posynomiality Proof**

$\blacksquare$  Is  $\mu_2$  a posynomial function of wire widths?

$$\mathbf{m}_2 = 2m_2 - m_1^2$$

- □ m<sub>1</sub> and m<sub>2</sub> in an RC tree are posynomial functions of wire widths

- $\blacksquare$  Prove by induction:  $\mu_2$  of RC tree response is a posynomial function of wire widths

#### For Inductive Interconnect

- High order moments for RCL circuits:

- M<sub>2</sub> is not guaranteed to be positive for RCL circuit responses

$$m_{2,k} = \sum_{i \in P(k)} R_i \sum_{j \in D(i)} m_{1,j} - \sum_{i \in P(k)} L_i \sum_{j \in D(i)} C_j$$

- Modeling of on-chip inductance

- A simple linear model for embedded wire

$$L \approx \mathbf{m} t / w$$

$$R_k R_D C_L + \frac{1}{4} R_k^2 C_k \ge L_k$$

## **Sizing Formulations**

A posynomial interconnect sizing formulation with second order constraints:

(I)

$$\begin{aligned} & & minimize & Area(W) \\ & & subject \ to & m_{1,k}(W) \leq d_0 \\ & & and & \mu_{2,k}(W) \leq s_0 \\ & & and & \underline{w}_i \leq w_i \leq \overline{w}_i \quad i = 1,...N \end{aligned}$$

- □ The inequality constraints on  $\mu_2$  represent the constraints on signal quality

- □ Attenuation:  $a(w) = -10\log(1 m_2w^2) \le a_0$

- □ Transition time:  $TR = \sqrt{2p \, m}_2 \le TR_0$

## **Sizing Formulations**

For clock tree sizing problems, the delay constraints are equality constraints in order to achieve zero skew solutions

```

minimize Area(W)

subject to m_{I,k}(W) = d_0

and \mu_{2,k}(w) \le s_0

and w_i \le w_i \le \overline{w_i} i = 1,...N

```

□ Given the posynomiality of the constraints, the above problem can be solved via a multistage approach. Each stage involves solving a problem of (I). [Celik99][Kay97]

## **Sizing Formulations**

The posynomiality can be applied to other type of sizing formulations

(II)

$$\begin{array}{lll} & minimize & Max\ delay\ (W\ ) & subject\ to & Area\ (W\ ) \leq a_0 & \\ & and & \mu_{2,k}\ (W\ ) \leq s_0 & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq \overline{w_i} \quad i=1,...N & \\ & and & w_i \leq w_i \leq w_i \leq w_i & \\ & and$$

Sizing formulations (I) and (II) are both posynomial programs as the Elmore delay based sizing problems

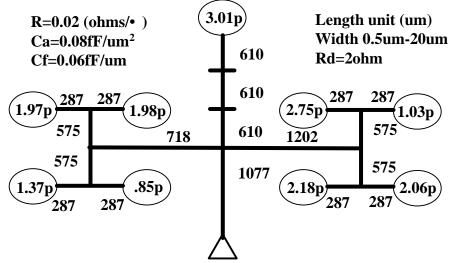

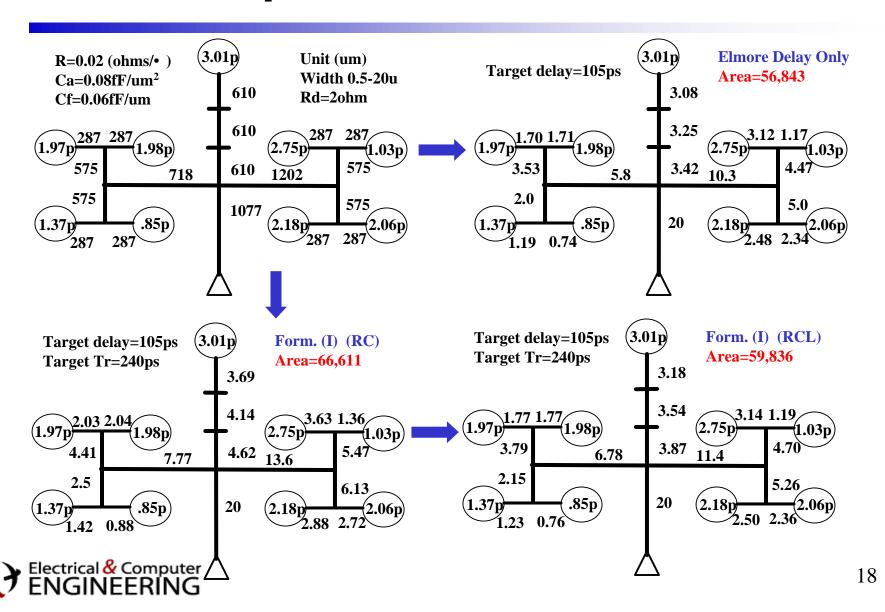

#### **Experiments**

- Extend sequential quadratic programming wire sizing algorithm (ORCIDS)

- Provable convergence

- $\square$  Compute  $\mu_2$  in o(n) complexity by path tracing

- Match the second order moments of transmission line models [Yu95]

- Example:

- Design Constraints:

$$Delay \leq 105 \quad ps$$

$$TR \leq 240 \quad ps$$

# **Experiment Results**

#### **Conclusions**

- The second central moment is a posynomial metric of interconnect signal integrity

- Interconnect sizing problems with second order signal integrity constraints are formulated as posynomial programs

- The existing algorithms can be extended to solve the new sizing problems with provable convergence