# From Academic Ideas to Practical Physical Design Tools

Ren-Song Tsay ISPD, March 2011

### My Family

National Tsing-Hua University, Taiwan

#### UC Berkeley

# 1994 IEEE Transaction CAD Best Paper Award

#### Physical Design System

ArcGate – Astro: the first commercially successful performance optimization physical design system

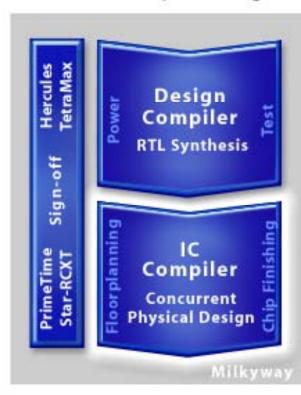

Galaxy Design Platform Concurrent Physical Design

## Reconfigurable Computer for Semulation

a breakthrough logic verifications (Simulation/Emulation) system

Cadence Incisive

Xtreme series

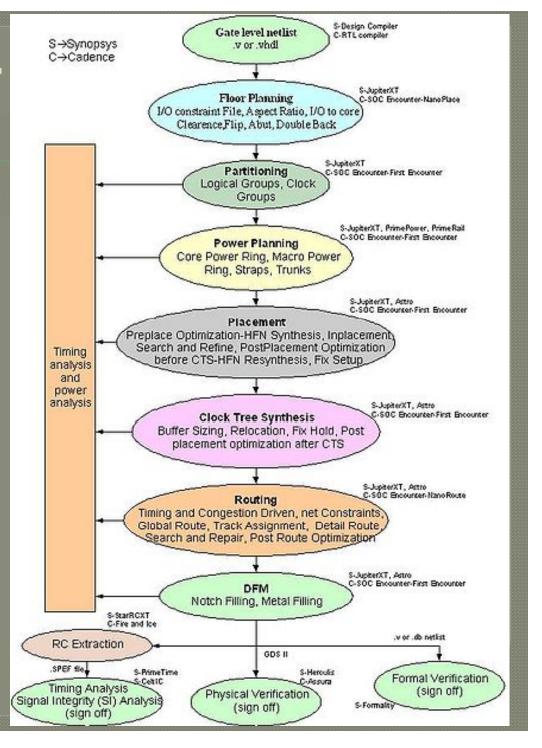

### Wiki Physical Design Flow

#### Pao-Ding

### Physical Design Optimization

#### Physical Design Optimization

- Routability

- No design rule violations

- Performance

- clock period

- Low power

Floorplan

Placement

Routing

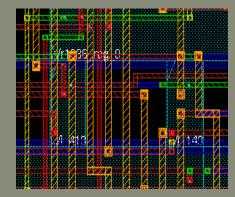

### A Progressive Design Methodology

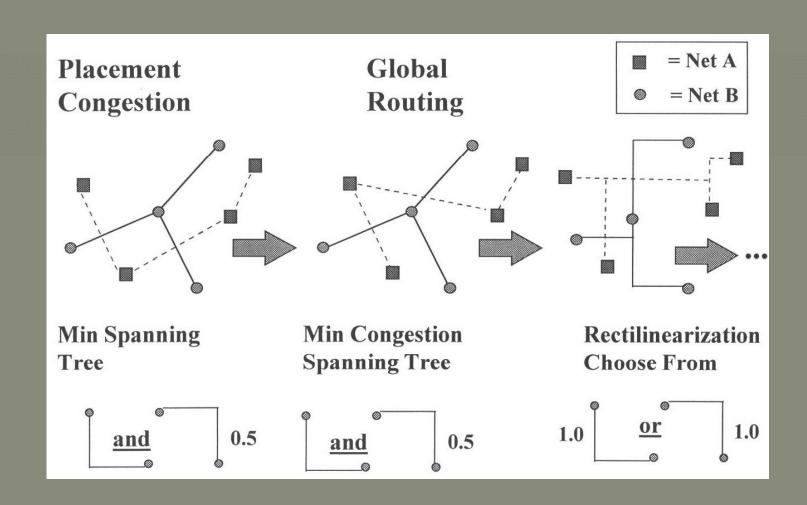

**Placement**

Global Routing

**Detailed Routing**

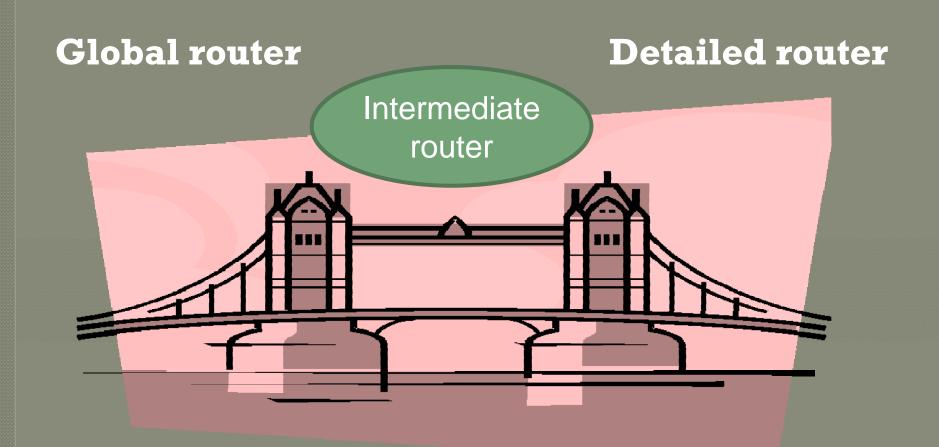

ArcGate Approach:

Placement

Global Routing

Intermediate Routing

**Detailed Routing**

- Lookahead

- Feedback

#### A Progressive Optimization Example

#### PROUD Quadratic Placement

$$\min\{L = \frac{1}{2} \sum_{i,j} c_{ij} (x_i - x_j)^2 \mid \forall n_{ij} \in N\}$$

- Convex contour of the cost function

- Recursive partitioning

- Min-cut improvement

- First-order constraint

- Detailed placement improvement

- Pair-wise interchange

- Single cell movement

- Rotation/flipping

#### Progressive optimization

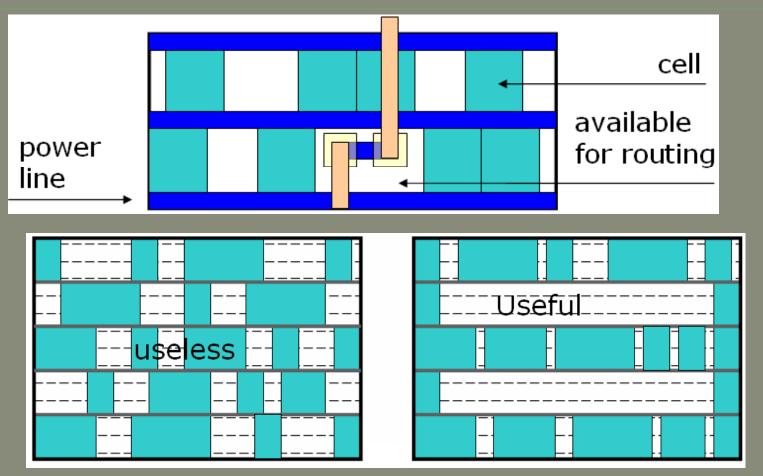

#### Cell Porosity & Pin Access

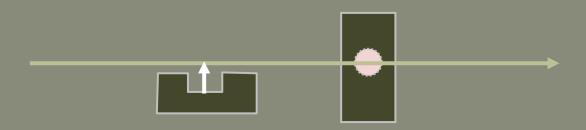

#### Estimate Chip Height and Width

The number of required routing tracks should satisfy H/V cut-demands

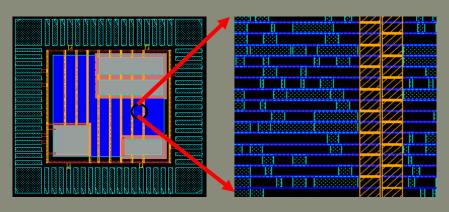

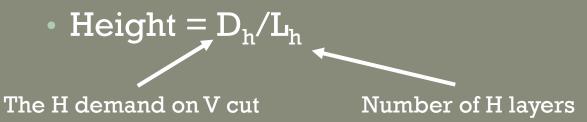

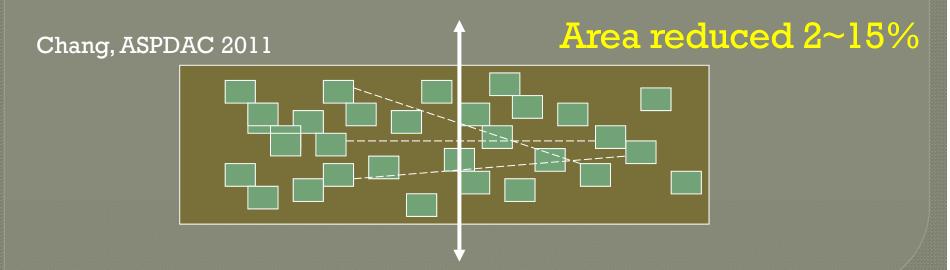

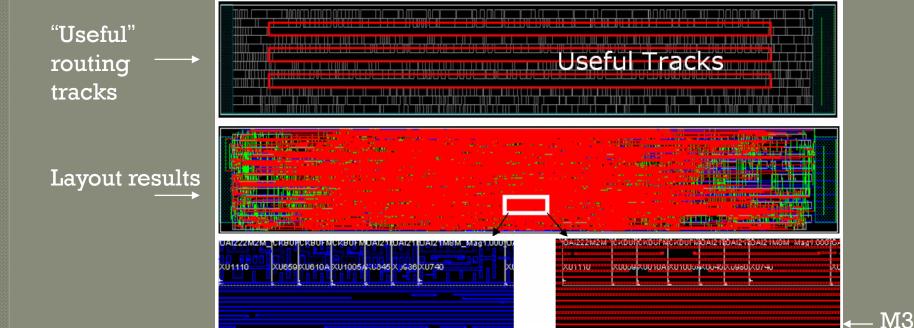

#### Align Useful M1 Routing Tracks

Runtime 5.3 x faster

#### A Test Result of M1 Alignment

M1

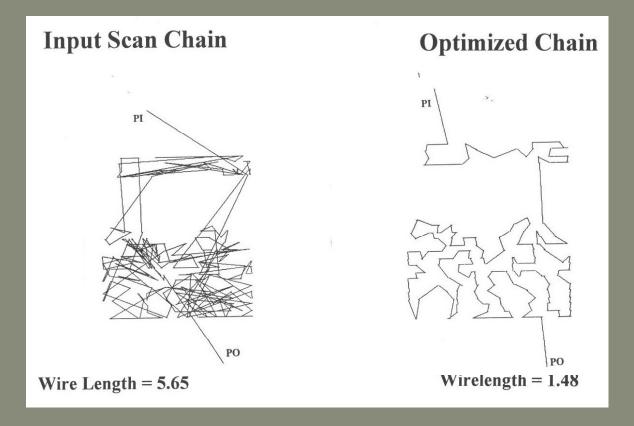

#### Scan Chain Optimization

Greatly improve wirability and timing performance

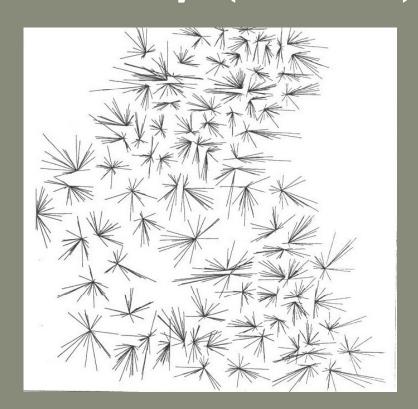

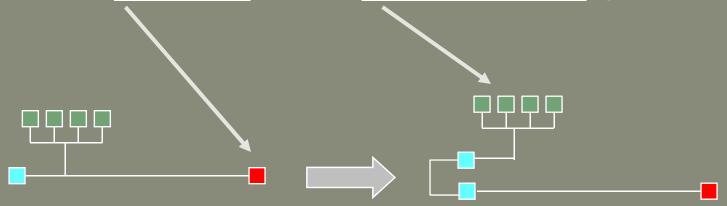

#### Optimal Clock Tree Synthesis

Balance wire, load and phase delays (of macros)

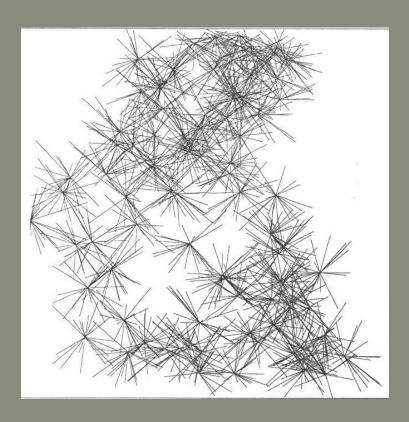

Before optimization

After optimization

#### LEQ Port Optimization

Critical path

Switch to faster internal edge

Faster edge

## Timing Optimization

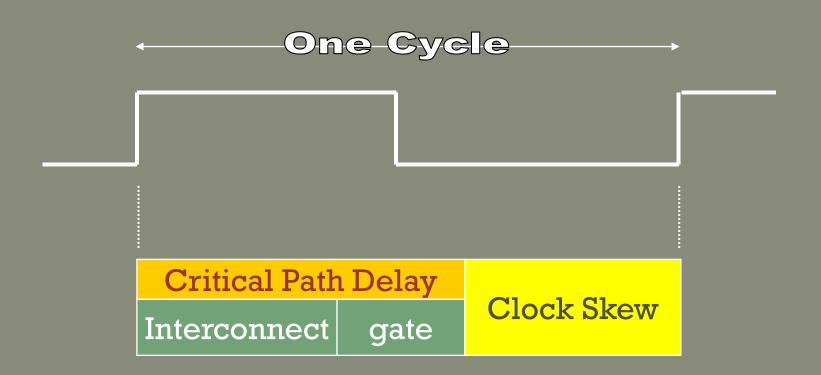

#### Timing-Driven: Min Cycle Time

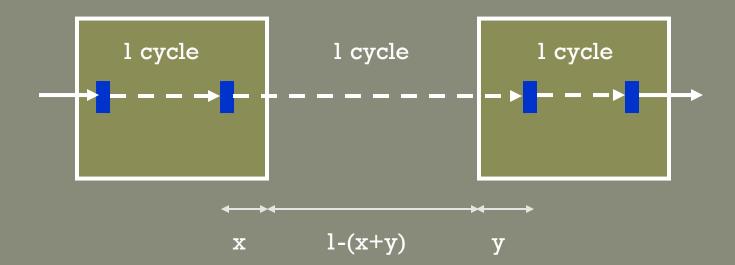

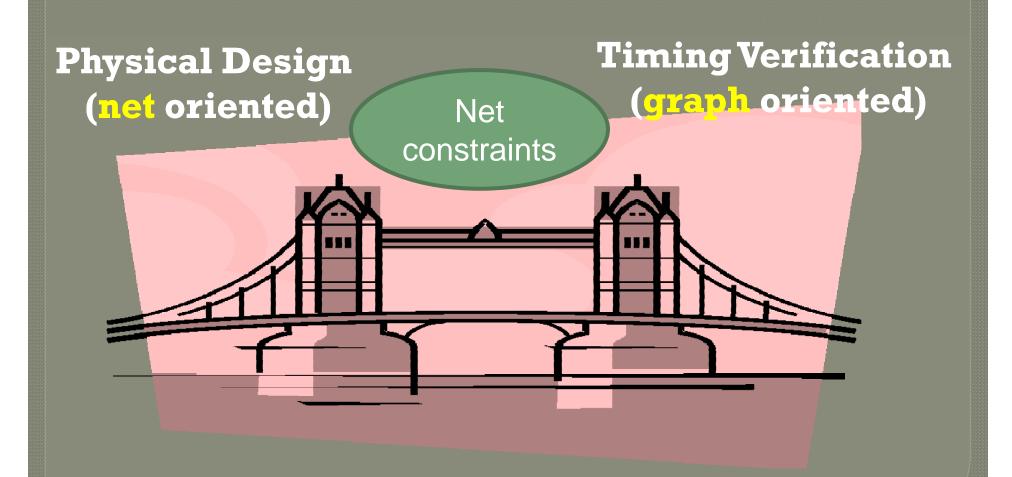

#### Design Plan Timing Budgeting

Main issue: cross-macro timing paths

#### Net Splitting

Separate critical from non-critical group

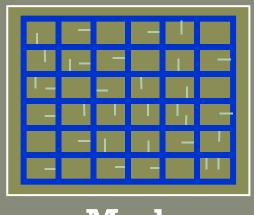

#### Clock Network Styles

Mesh

H-Tree

**C-Tree**

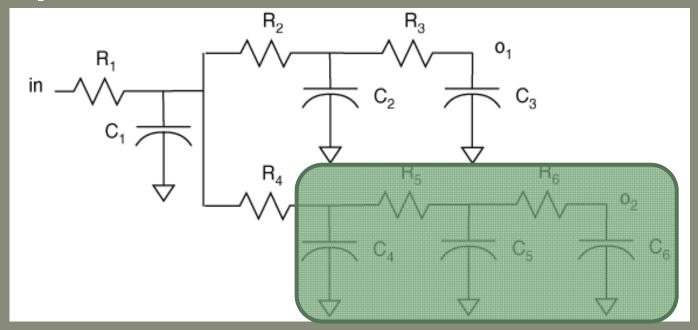

#### Elmore delay

$$t_4 = R_4(C_4 + C_5 + C_6)$$

$$C_{eq} = C_4 + C_5 + C_6$$

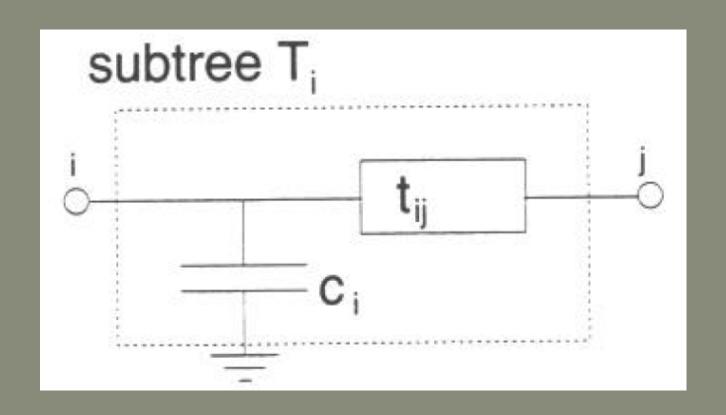

## An equivalent lumped delay model of a clock subtree

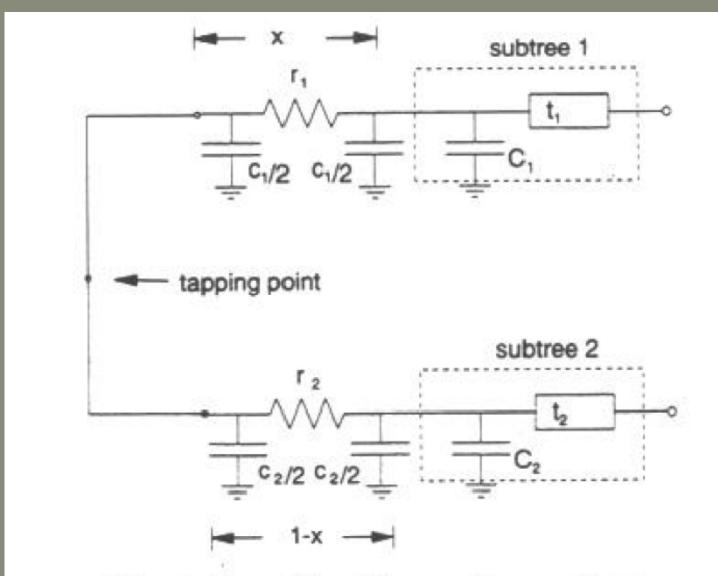

Fig. 5. Zero-Skew Merge of two subtrees.

#### Find Zero Skew Point

Solve [rl=xl, r2 = (l-x)l]

$$r_1(c_1/2 + C_1) + t_1 = r_2(c_2/2 + C_2) + t_2$$

Get

$$x = \frac{(t_2 - t_1) + \alpha l \left(C_2 + \frac{\beta l}{2}\right)}{\alpha l (\beta l + C_1 + C_2)}.$$

#### Practical Clock Route Consideration

Routing Blockages

Avoid Pin Access Blocking

## Timing Optimization

#### Bridging

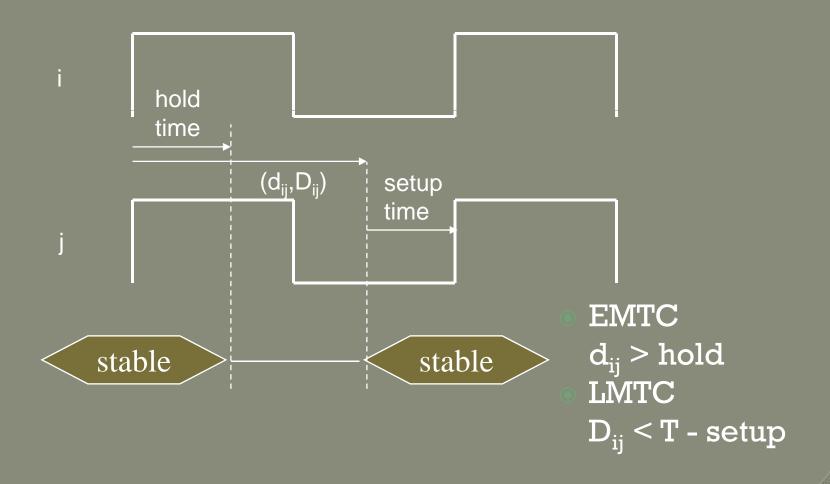

#### Timing Constraints

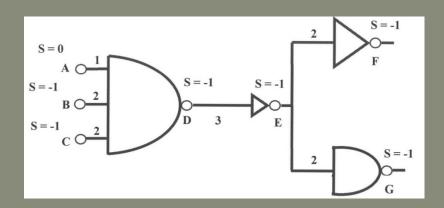

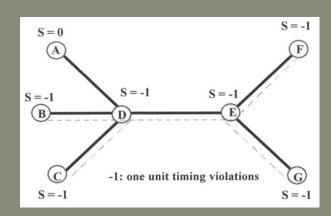

## Timing Slack Graph

- A snap shot of the timing verification result in terms of a slack number on each pin and edge.

- It actually contains both timing and connectivity information.

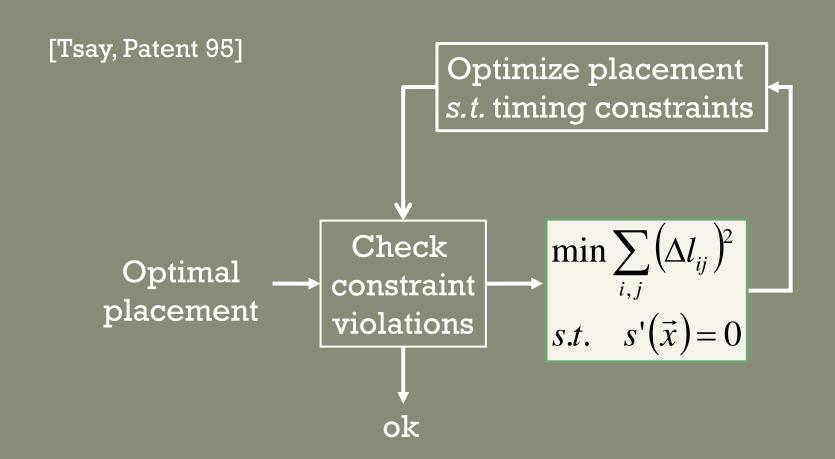

#### TDP by Minimum Perturbation

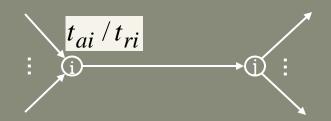

## Slack and Delta Improvement

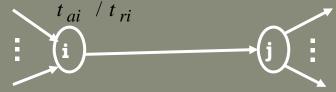

$$s_i = t_{ri} - t_{ai}$$

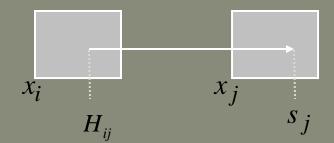

... nodal slack  $H_{ij} = t_{rj} - \left(t_{ai} + d_{ij}\right)$  ... edge slack, where  $d_{ij} =$  edge delay Define:  $x_i = t_{ai} - t_{ai}$  ... arrival time improvement at node i  $y_j = t_{rj}^{'} - t_{rj}$  ... required arrival time improvement at node j

#### Incremental Slack Calculation

$$s'_{i} = t'_{ri} - t'_{ai} = (t_{ri} + y_{i}) - (t_{ai} - x_{i})$$

=  $(t_{ri} - t_{ai}) + (x_{i} + y_{i}) = s_{i} + (x_{i} + y_{i})$

similarly,

$$H'_{ij} = H_{ij} + x_i + y_j - \Delta d_{ij}$$

where,

$$d_{ij}' = d_{ij} + \Delta d_{ij}$$

#### Zero-Slack on Active Constraints

At node i:

$$|x_i + y_i + s_i = 0 \implies y_i = -(x_i + s_i)|$$

At edge ij:

$$x_i + y_j - \Delta d_{ij} + H_{ij} = 0 \implies \Delta d_{ij} = (x_i + H_{ij}) - (x_j + s_j)$$

#### Minimum Placement Perturbation

Assume local placement change

$$\Delta l_{ij} = \Delta d_{ij} / (R_i c + r C_j)$$

Hence

$$\min \sum_{i,j} (\Delta l_{ij})^2 = \min \sum_{i,j} (\Delta d_{ij} / (R_i c + rC_j))^2$$

$$= \min \sum_{i,j} \frac{1}{(R_i c + rC_j)^2} [(x_j + s_j) - (x_i + H_{ij})]^2$$

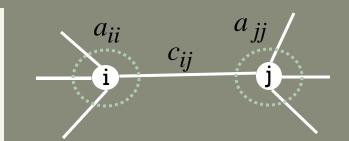

#### Equivalent to Quadratic Placement

$$\min \sum_{i,j} (\Delta l_{ij})^2 = \min \sum_{i,j} \frac{1}{D_{ij}^2} \left[ (x_j + s_j) - (x_i + H_{ij}) \right]^2$$

$$\text{Pin offset}$$

$$\text{connectivity}$$

\* Then take  $(l_{ij} + \Delta l_{ij})$  as the upper bound constraint

#### Net Weighting Placement Approach

$$\min\{L = \frac{1}{2} \sum_{i,j} c_{ij} x_{ij}^2 \mid x_{ij}^2 \le u_{ij}^2, \forall n_{ij} \in N\}$$

Tsay, DAC 90

- Can solve by applying necessary and sufficient Kuhn-Tucker conditions => Lagrange Multiplier = "added net weighting"

- ◆Approximated Solution

$$\lambda_{ij} = \left(\frac{\frac{\left(x_{ij} - u_{ij}\right)}{u_{ij}}}{\frac{1}{a_{ii}} + \frac{1}{a_{jj}} - \frac{2c_{ij}}{a_{ii}a_{jj}}}\right)$$

## Cell Sizing

- Minimize total cell size while meeting timing constraints

- optimize timing on critical paths

- size down in non-critical paths

- Experiments show 30~40% performance gain, with reduced total cell area

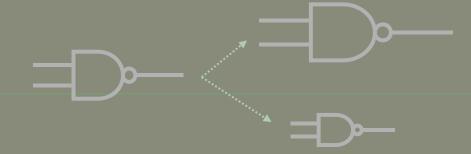

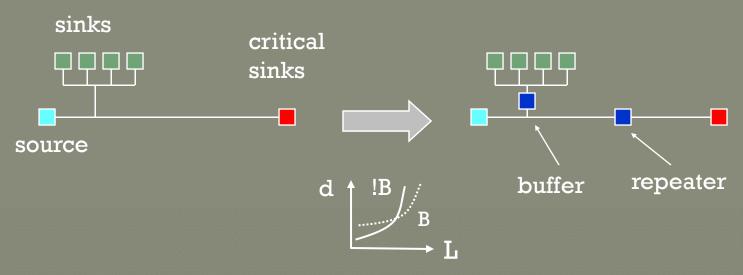

#### Buffer/Repeater Insertion

- ✓ Buffer blocks off unnecessary capacitance load to critical sink.

- ✓ Repeater reduces "quadratic" interconnect delay.

# Timing-Driven Example

#### 7K cells

| TDP | TDR | Relative cycle time |

|-----|-----|---------------------|

| _   |     | 1.00                |

|     | _   | 0.58                |

| _   |     | 0.74                |

|     |     | 0.40                |

# Progressive Optimization