# Double Patterning Layout Decomposition for Simultaneous Conflict and Stitch Minimization

#### Kun Yuan, Jae-Seok Yang, David Z. Pan

Dept. of Electrical and Computer Engineering

The University of Texas at Austin

Sponsored in Part by NSF, SRC, Sun, Qualcomm, and equipment donations from Intel

#### Outline

- Background and Motivation

- Simultaneous Conflict and Stitch Minimization

- Grid Model

- Basic ILP formulation

- Speed-Up techniques

- Experimental Result

- Conclusion

## Lithography Challenges

◆ Aggressive scaling of min. printable half pitch HP

$$HP = k_1 \frac{\lambda}{NA}$$

KrF (248nm) 0.85NA 0.6 ArF (193nm) 0.5 ArFi 0.85NA k<sub>1</sub> 0.4 2D Practical Limit 1.35NA 0.3 1D Practical Limit 0.93NA ..... 0.2 0.1 0 130nm 90nm 65nm 45nm 32nm Logic technology node

k1: process difficulty

NA: numerical aperture —

λ: wavelength of source

♦ NA = 1.8, close to the limit

♦ EUV(13.5nm)

not available in near future

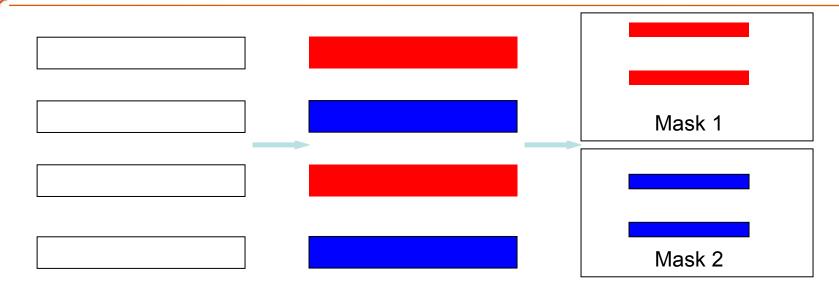

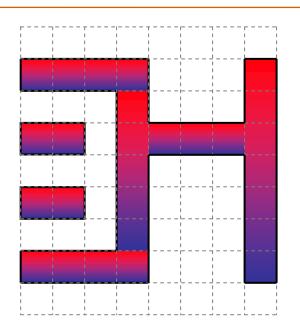

## Double Patterning Lithography (DPL)

- Most likely lithography solution for 32nm and beyond

- A layout is decomposed into two masks (colors)

- The effective pitch is doubled

- Manufactured through 2x exposures/etches.

Layout Decomposition.

However, it is NOT a trivial task

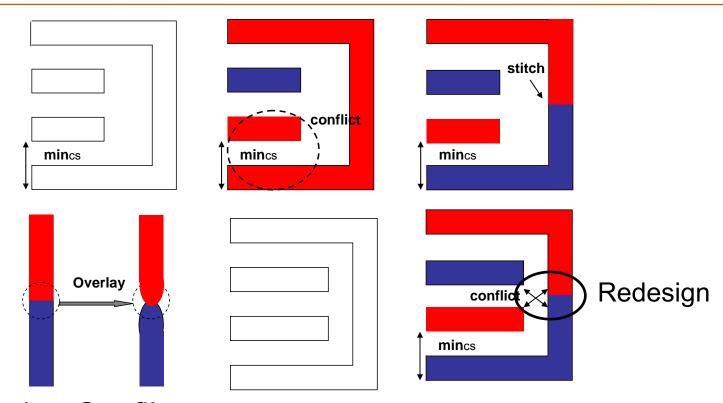

## Layout Decomposition Challenges

- Coloring Conflict:

- Two features within minimum coloring spacing should be colored different

- Splitting Stitch

- May resolve the conflict but cause yield loss due to overlay.

## **Existing Work**

- Heuristic approaches [Drapeau+, SPIE 2007]

- Greedy coloring and splitting in two stages

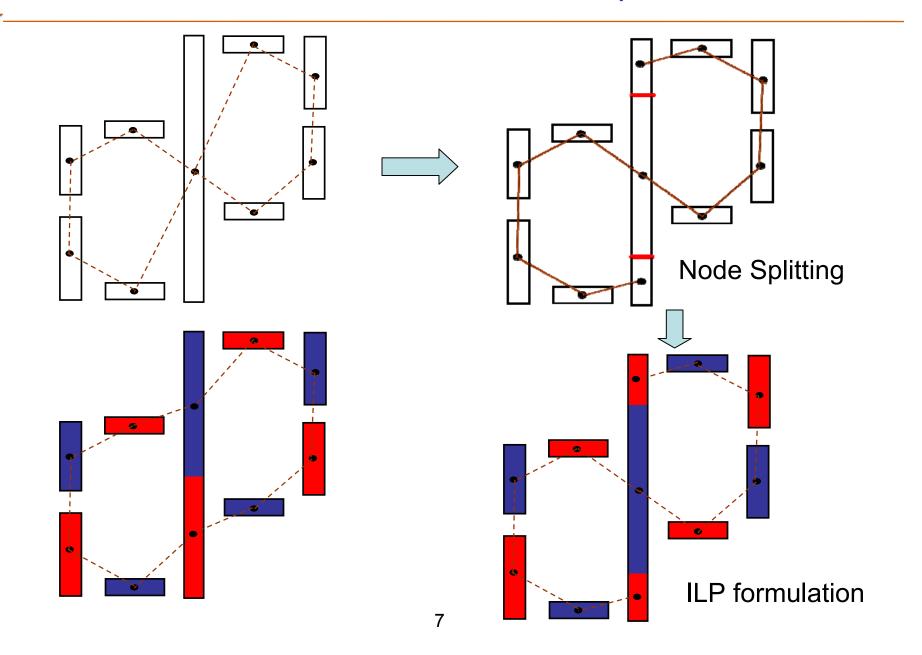

- ILP based layout decomposition [Kahng+, ICCAD 2008]

- Layout fracturing.

- Detect the uncolorable conflict cycle with odd number of nodes, and remove them by splitting the features

- > ILP is then applied to minimize the number of stitches.

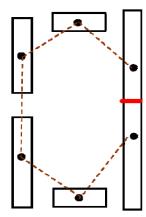

## Motivation for Simultaneous Optimization

#### Outline

- Background and Motivation

- Simultaneous Conflict and Stitch Minimization

- Grid Model

- Basic ILP formulation

- Speed-Up techniques

- Experimental Result

- Conclusion

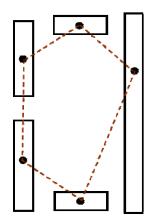

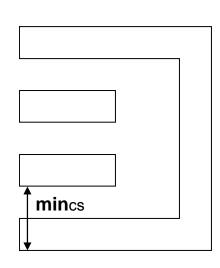

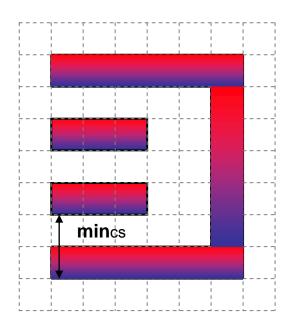

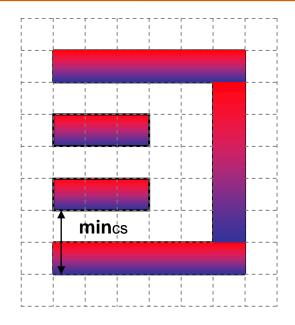

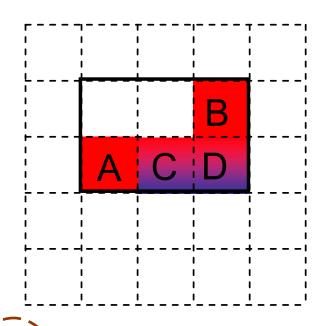

#### **Grid Model**

- Map the layout into grids

- > The size of each grids is half of the pitch of the original design

- Offer sufficient stitch candidates for large solution space

- Minimize the conflict and stitch between layout grids

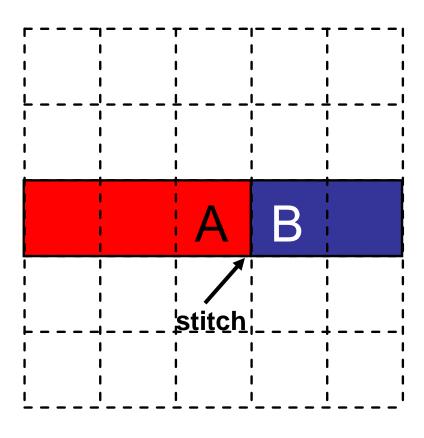

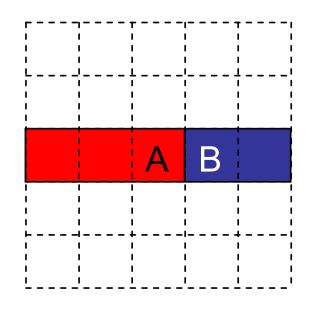

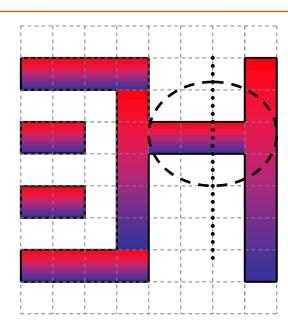

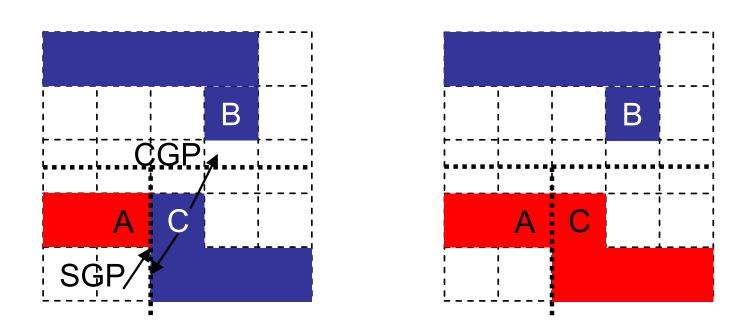

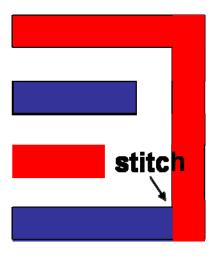

## Stitch Grid Pair (SGP)

Adjacent grids A and B are assigned to different masks

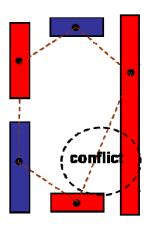

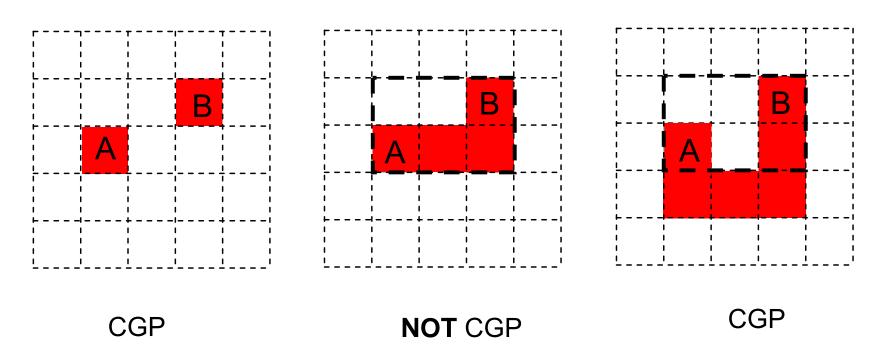

## Conflict Grid Pair (CGP)

- Two grids within minimum coloring distance are assigned into the same mask

- Boundingbox-Connected (BB-connected) case should be excluded.

#### **Basic ILP Formulation**

#### Coloring binary variable

$$x_i = 1 \text{ (Red)}, 0 \text{ (Blue)}$$

i is the unique id of each grid

#### Objectives

$$Min\left(\sum_{s_{i,j} \in SP} s_{i,j} + \alpha \sum_{c_{m,n} \in CP} c_{m,n}\right)$$

Binary variables  $s_{i,j}$  and  $c_{m,n} = 1$  if there is a SGP and CGP respectively SP or CP are the set of the grid pairs which could form a SGP or CGP.

#### **Detect SGP**

#### Logic equations

$$\frac{x_a \overline{x_b}}{\overline{x_a} x_b} = 1 \quad \Rightarrow \quad s_{a,b} = 1 \\

\overline{x_a} x_b = 1 \quad \Rightarrow \quad s_{a,b} = 1$$

#### Linear Constraints

$$x_a + (1 - x_b) \le 1 + s_{a,b}$$

$$(1 - x_a) + x_b \le 1 + s_{a,b}$$

$$x_i = 1 \text{ (Red)}, 0 \text{ (Blue)}$$

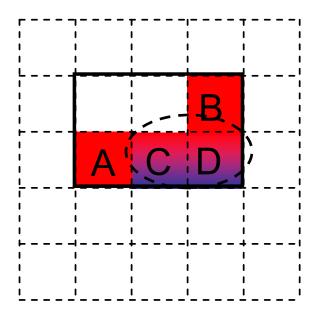

#### **Detect CGP**

#### Logic equations

$x_a x_b = 1 \&\& \text{ No RED BB-connected}$

$$\Rightarrow c_{a,b} = 1$$

$\overline{x_a} \overline{x_b} = 1$  && No BLUE BB-connected

$$\Rightarrow c_{a,b} = 1$$

#### Linear Constraints

$$x_a + x_b \le 1 + c_{a,b} + \sum_k r_{a,b}^k$$

$$(1 - x_a) + (1 - x_b) \le 1 + c_{a,b} + \sum_{k} b_{a,b}^k$$

Binary variables  $r_{a,b}^k$  and  $b_{a,b}^k = 1$

if there is BB-connected in RED and BLUE respectively

$$\sum_{k}$$

: The set of possible BB-connected paths.

$$x_i = 1 \text{ (Red)}, 0 \text{ (Blue)}$$

$r_{a,b}^1$ : Grids C and D are Red  $b_{a,b}^1$ ; Grids C and D are Blue

#### Detect BB-connected case

#### Logic Equation

$$r_{pq,uv}^k = \prod_{x_{e,f} \in P_{pq,uv}^k} x_{e,f}$$

$$e.g. r_{a,b}^{1} = x_{c}x_{d}$$

#### Linear Constraints

$$\sum_{x_{e,f} \in P_{pq,uv}^k} x_{e,f} \leq \left(n_{pq,uv}^k - 1\right) + r_{pq,uv}^k$$

$$\sum_{x_{e,f} \in P_{pq,uv}^k} (1 - x_{e,f}) \le n_{pq,uv}^k \left( 1 - r_{pq,uv}^k \right)$$

$n_{pq,uv}^{k}$  is the number of grids in the path

$$x_i = 1 \text{ (Red)}, 0 \text{ (Blue)}$$

$$x_c + x_d \le (2-1) + r_{a,b}^1$$

$$(1-x_c) + (1-x_d) \le 2(1-r_{a,b}^1)$$

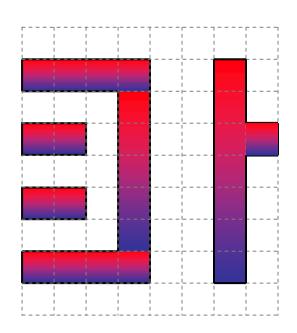

## Speed-Up Techniques: Independent Component Computation

- Independent Components: Isolated layout clusters without possible SGP and CGPs between them.

- They can be solved individually, and the solution can be simply merged without losing optimality in terms of ILP objectives.

## Speedup Techniques: Layout Partition

- There could still be large design which has prohibitive problem size even after independent component computation

- We can apply min-cut partition to divide a large components to several small connected ones

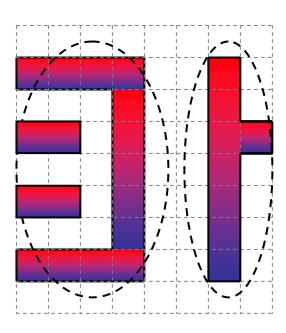

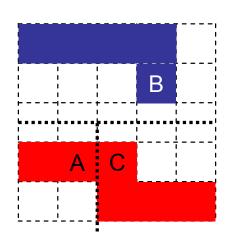

## Coloring Flipping for Layout Partition

We can flip the coloring of certain partition to obtain better resolution across the boundaries

## ILP Formulation for Coloring Flipping

#### Binary Variable

$f_i = 0$  (Not flipped), 1 (Flipped) for partition i  $f_{i,j} = 0$  if both i and j flip or do not flip  $f_{i,j} = 1$  if only one of i and j flips

#### Objective

$$\min \sum (f_{i,j}(s_{i,j}^{e0} + \alpha c_{i,j}^{e})) + (1 - f_{i,j})(s_{i,j}^{e1} + \alpha c_{i,j}^{e1})$$

$s_{i,j}^{e0/e1}$  and  $c_{i,j}^{e0/e1}$  are the stitch and conflict crossing the boundary

#### Constraints

$$f_{i,j} = f_i f_j + \overline{f_i} \overline{f_j}$$

## **Experimental Setup**

- Implement in C++.

- Comparative two-phase approach

- First Phase:

- » Color all the layout polygons sequentially.

- » Assign colors to minimize current conflicts.

- Second Phase:

- » Detect the coloring conflict segments

- » Flip the coloring these segments to resolve the conflicts.

### Benchmark

## Eight scaled testcases

| Circuit | Area(µm²) | Grid size | Layout grids |

|---------|-----------|-----------|--------------|

| c1      | 89        | 294x294   | 6670         |

| c2      | 160       | 395x395   | 15710        |

| с3      | 207       | 450x450   | 20496        |

| c4      | 292       | 534x534   | 33497        |

| c5      | 422       | 642x642   | 53998        |

| с6      | 540       | 726x726   | 68820        |

| с7      | 747       | 854x854   | 101431       |

| c8      | 1028      | 1002x1002 | 142535       |

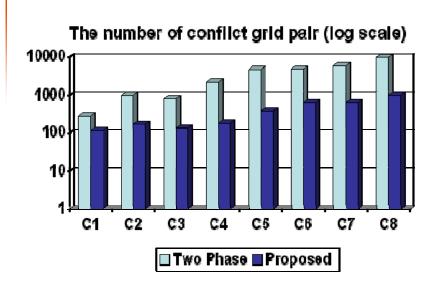

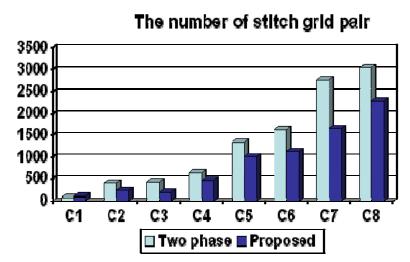

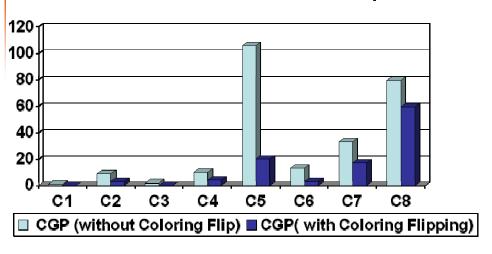

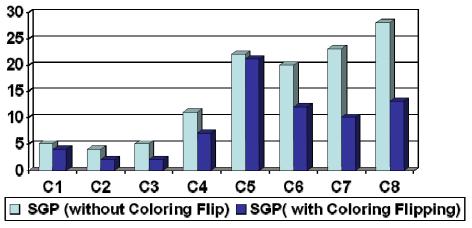

## Coloring Conflict and Splitting Stitch

8x reduction on coloring conflict

33% less stitches

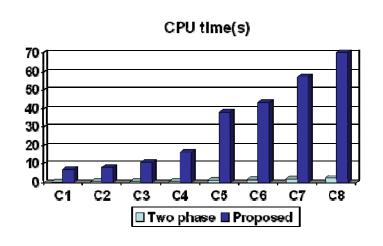

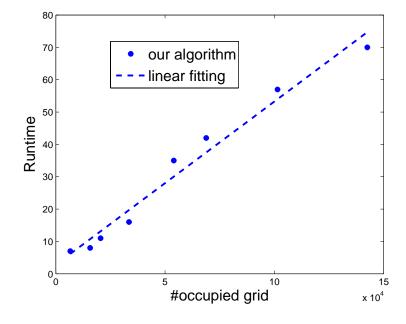

## Scalability

The runtime is in reasonable scope.

The complexity shows

linearity with number of occupied grids in test cases

#### Conclusion

- Double patterning layout decomposition for simultaneous conflict and stitch minimization

- Grid model, integer linear programming, Independent component computation, layout partition

- Explore DPL-friendly design methodology

- DPL-aware detailed routing with redundant via consideration.

- DPL-aware standard cell design.

- Special thanks to Dr. Minsik Cho at IBM research

## BackUp

## Coloring Flipping

## The number of conflict grid pair across the boundaries of different partitions

70% less conflicts

## The number of stitch grid pair across the boundaries of different partitions

40% less stitches

## ILP Constraints for Coloring Flipping

#### Logic equations

$$f_{i,j} = f_i f_j + \overline{f_i} \overline{f_j}$$

Linear Constraints

$$\begin{aligned}

f_i f_j &\leq f_{i,j} \\

\overline{f_i f}_j &\leq f_{i,j} \\

f \overline{f_j} &\leq f_{i,j} \\

f \overline{f_j} &\leq \overline{f_{i,j}} \\

\hline

f_i f_j &\leq \overline{f_{i,j}} \\$$